# Autoencoders on field-programmable gate arrays for real-time, unsupervised new physics detection at 40 MHz at the Large Hadron Collider

Ekaterina Govorkova<sup>®</sup><sup>1</sup><sup>⊠</sup>, Ema Puljak<sup>®</sup><sup>1</sup>, Thea Aarrestad<sup>®</sup><sup>1</sup>, Thomas James<sup>1</sup>, Vladimir Loncar<sup>®</sup><sup>1,2</sup>, Maurizio Pierini<sup>®</sup><sup>1</sup>, Adrian Alan Pol<sup>®</sup><sup>1</sup>, Nicolò Ghielmetti<sup>1,3</sup>, Maksymilian Graczyk<sup>1,4</sup>, Sioni Summers<sup>1</sup>, Jennifer Ngadiuba<sup>®</sup><sup>5,6</sup>, Thong Q. Nguyen<sup>6</sup>, Javier Duarte<sup>®</sup><sup>7</sup> and Zhenbin Wu<sup>8</sup>

To study the physics of fundamental particles and their interactions, the Large Hadron Collider was constructed at CERN, where protons collide to create new particles measured by detectors. Collisions occur at a frequency of 40 MHz, and with an event size of roughly 1 MB it is impossible to read out and store the generated amount of data from the detector and therefore a multi-tiered, real-time filtering system is required. In this paper, we show how to adapt and deploy deep-learning-based autoen-coders for the unsupervised detection of new physics signatures in the challenging environment of a real-time event selection system at the Large Hadron Collider. The first-stage filter, implemented on custom electronics, decides within a few microseconds whether an event should be kept or discarded. At this stage, the rate is reduced from 40 MHz to about 100 kHz. We demonstrate the deployment of an unsupervised selection algorithm on this custom electronics, running in as little as 80 ns and enhancing the signal-over-background ratio by three orders of magnitude. This work enables the practical deployment of these networks during the next data-taking campaign of the Large Hadron Collider.

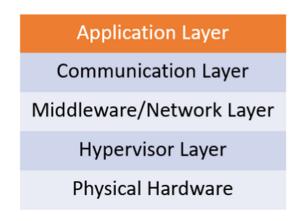

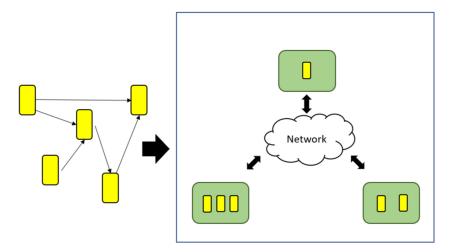

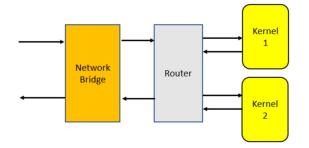

roton-proton collision events occur 40 million times per second at the particle detectors at the CERN Large Hadron Collider (LHC)<sup>1</sup>. The largest general-purpose particle detectors at the LHC, ATLAS<sup>2</sup> and CMS<sup>3</sup>, discard most of the collision events with online selection systems, as a result of bandwidth limitations. These systems consist of two stages: the level-1 trigger (L1T)<sup>4-7</sup>, where algorithms are deployed as programmable logic on custom electronic boards equipped with field-programmable gate arrays (FPGAs), and the high-level trigger (HLT), where selection algorithms asynchronously process the events accepted by the L1T on commercially available CPUs. The event rate is reduced from 40 MHz to around 100 kHz within a few microseconds at the first selection stage, L1T. When designing searches for collisions containing new physics (for example, dark matter production), physicists typically consider specific scenarios motivated by theoretical considerations. This supervised strategy has proven to be successful when dealing with theory-motivated searches, as was the case with the search for the Higgs boson<sup>8,9</sup>. Conversely, this approach may become a limiting factor in the absence of a strong theoretical prior. For this reason, there are several community efforts to investigate unsupervised machine learning (ML) techniques for new physics searches<sup>10,11</sup>. These investigate the use of autoencoders (AEs) and variational autoencoders (VAEs) for offline processing<sup>12,13</sup>, and therefore do not consider constraints such as resource use and latency. Early suggestions to use AEs in HEP for anomaly detection<sup>14,15</sup> are not easily adapted to an L1T environment. For instance, refs. <sup>14,15</sup> require access to the momenta of all jet particle constituents, something that is not available now and will only be partly available (for example, first eight candidates) in the future. Refs. <sup>16,17</sup> propose integrating unsupervised learning algorithms in

the online selection system of the CMS and ATLAS experiments, in order to preserve rare events that would not otherwise be selected, in a special data stream.

While the primary focus for online unsupervised learning so far has been for the HLT, this strategy could be more effective if deployed in the L1T, that is, before any selection bias is introduced. Due to the extreme latency and computing resource constraints of the L1T, only relatively simple, mostly theory-motivated selection algorithms are currently deployed. These usually include requirements on the minimum energy of a physics object, such as a reconstructed lepton or a jet, effectively excluding lower-energy events from further processing. Instead, by deploying a new-physics model agnostic algorithm that selects events based on their degree of abnormality, we can collect data in a signal-model-independent way. Such an anomaly detection (AD) algorithm is required to have extremely low latency because of the restrictions imposed by the L1T.

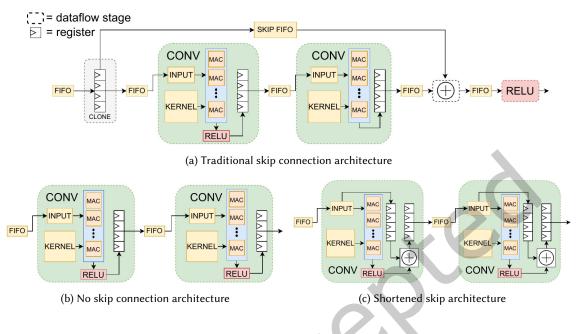

Many recent efforts for translating ML algorithms into FPGA firmware are reviewed extensively in refs.<sup>18–20</sup>. However, many of these toolflows result in implementations that are not optimized for the L1T systems or do not apply to HEP AE architectures. For example, FINN<sup>21,22</sup> focuses on dataflow-style implementations of convolutional neural networks (CNNs), which may not achieve the low latency and high throughput required for L1T applications. It is by construction limited to Xilinx FPGAs, while hls4ml backends targeting different HLS libraries (Quartus for Intel and Katapult for ASIC design) are under development. Other efforts, Conifer<sup>23</sup> (also developed by the hls4ml team) and fwXmachina<sup>24</sup>, feature a custom implementation of boosted decision trees on FPGAs, which achieves the desired L1T constraints, but does not extend to neural network implementations.

<sup>&</sup>lt;sup>1</sup>European Organization for Nuclear Research (CERN), Geneva, Switzerland. <sup>2</sup>Institute of Physics Belgrade, Belgrade, Serbia. <sup>3</sup>Politecnico di Milano, Milan, Italy. <sup>4</sup>Imperial College London, London, UK. <sup>5</sup>Fermi National Accelerator Laboratory, Batavia, USA. <sup>6</sup>California Institute of Technology, Pasadena, USA. <sup>7</sup>University of California San Diego, La Jolla, USA. <sup>8</sup>University of Illinois at Chicago, Chicago, USA. <sup>5</sup>Re-mail: katya.govorkova@cern.ch

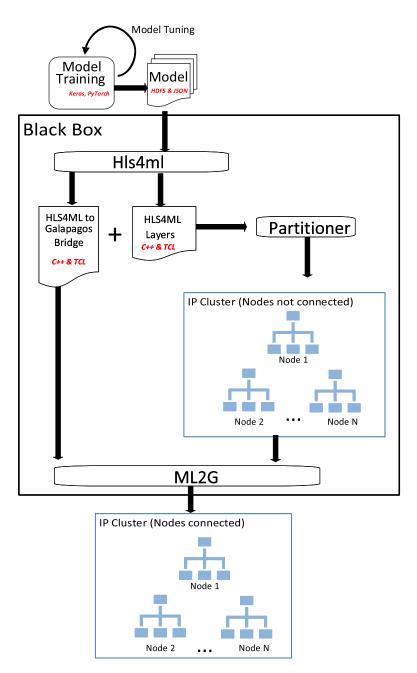

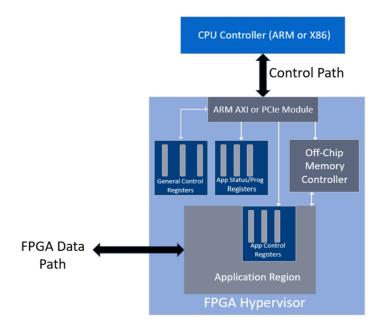

Recent developments of the hls4ml library allow us to consider the possibility of deploying AE-based AD algorithms on the FPGAs mounted on the L1T boards. The hls4ml library is an open-source software, developed to translate neural networks<sup>25-29</sup> and boosted decision trees<sup>30</sup> into FPGA firmware. A fully on-chip implementation of the ML model is used in order to stay within the 1µs latency budget imposed by a typical L1T system. Additionally, the initiation interval (II) of the algorithm should be within 150ns, which is related to the bunch-crossing time for the upcoming period of the LHC operations<sup>5</sup>. Since there are several L1T algorithms deployed per FPGA, each of them should use much less than the available resources. With its interface to QKERAS<sup>31</sup>, hls4ml supports quantization-aware training (QAT)<sup>32</sup>, which makes it possible to drastically reduce the FPGA resource consumption while preserving accuracy. Using hls4ml, we can compress neural networks to fit the limited resources of an FPGA.

The aim of this work is the development of a fast algorithm to define a dataset enriched in anomalies, without using physics-motivated expectations about new physics to define the anomaly. Once collected, these data could be visually inspected or analysed with model-agnostic techniques, for example, those proposed in refs.<sup>33,34</sup>, or even with traditional model-dependent searches (provided an understanding of the bias imposed by the online selection on the offline event distribution). We focus on AEs, with specific emphasis on VAEs<sup>12,13</sup>. We consider both fully connected and convolutional architectures, and discuss how to compress the model through pruning<sup>35-37</sup>, the removal of unnecessary operations, and quantization<sup>26,38-45</sup>, the reduction of the precision of operations.

As discussed in ref. <sup>16</sup>, one can train (V)AE on a given data sample by minimizing a measure of the distance between the input and the output (the loss function). This strategy, which is very common when using (V)AEs for anomaly detection<sup>46</sup>, brings practical challenges when considering a deployment on FPGAs. The use of high-level features is not optimal because it requires time-consuming data preprocessing. The situation is further complicated for VAEs, which require a random sampling from a Gaussian distribution in the latent space. Furthermore, one has to buffer the input data on chip while the output is generated by the FPGA processing in order to compute the distance afterwards. To deal with all of these aspects, we explore different approaches and compare the accuracy, latency and resource consumption of the various methods.

In addition, we discuss how to customize the model compression in order to better accommodate for unsupervised learning. Previously, we showed that QAT can result in a large reduction in resource consumption with minor accuracy loss for supervised algorithms<sup>28,32</sup>. In this paper, we extend and adapt that compression workflow to deal with the specific challenge of compressing autoencoders used for AD. Several approaches are possible:

- Post-training quantization (PTQ)<sup>25,36,47-50</sup>, consists of applying a fixed-point precision to a floating-point baseline model. This is the simplest quantization approach, typically resulting in good algorithm stability, at the cost of losing performance.

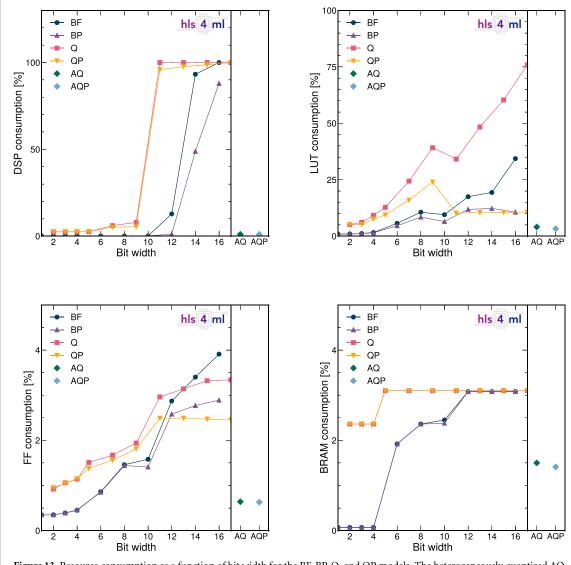

- QAT, consists of imposing the fixed-point precision constraint at training time, for example, using the QKERAS or Brevitas<sup>51</sup> libraries. This approach typically allows one to limit the accuracy loss when imposing a higher level of quantization, finding a better weight configuration than what one can get with PTQ.

- Knowledge distillation with QAT changes the quantized-model optimization strategy by reframing the problem as knowledge distillation <sup>52-55</sup>.

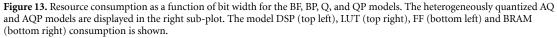

- Anomaly classification with QAT; approximated loss regression with QAT could be turned into a classification problem.

In this paper, we focus on the first two approaches, leaving the investigation of the other approaches to future work.

#### **Data samples**

This study follows the setup of refs. 16,56. The dataset (with its definition and limitations) are taken from ref.<sup>16</sup>. We adapt the data format to make it more consistent with inputs received in the L1T (as opposed to the HLT) and show that one can do at L1T what ref.<sup>16</sup> proposed for the HLT. Perhaps surprisingly, this is indeed possible due to recent progress made on deploying neural networks on FPGAs. We use a data sample that represents a typical protonproton collision dataset that has been pre-filtered by requiring the presence of an electron or a muon with a transverse momentum  $p_{\rm T}$ >23 GeV and a pseudo-rapidity  $|\eta|$  < 3 (electron) and  $|\eta|$  < 2.1 (muon). These requirements were introduced to reduce the dataset size to a manageable level, such that we could generate it with our limited computing resources. In a real-life application, no  $p_{\rm T}$ requirement of this kind would be applied. The  $\eta$  requirements would stay since they are intrinsic consequences of the detector geometry. In addition to the background-like sample, we consider the four benchmark new physics scenarios discussed in ref.<sup>16</sup>:

- A leptoquark (LQ) with a mass of 80 GeV, decaying to a b quark and a τ lepton <sup>57</sup>,

- A neutral scalar boson (A) with a mass of 50 GeV, decaying to two off-shell Z bosons, each forced to decay to two leptons: A→4ℓ<sup>58</sup>,

- A scalar boson with a mass of 60 GeV, decaying to two tau leptons:  $h^0 \rightarrow \tau \tau^{59}$ ,

- A charged scalar boson with a mass of 60 GeV, decaying to a tau lepton and a neutrino:  $h^{\pm} \rightarrow \tau \nu^{60}$ .

These four processes are used to evaluate the accuracy of the trained models. A detailed description of the dataset can be found in ref. <sup>61</sup>. In total, the background sample <sup>62</sup> consists of 8 million events. Of these, 50% are used for training, 40% for testing and 10% for validation.

#### Autoencoder models

We consider two classes of architecture: one based on dense feed-forward neural networks (DNNs) and one using CNNs. Both start from the  $(p_{T}, \eta, \phi)$  values for 18 reconstructed objects (ordered as 4 muons, 4 electrons and 10 jets), the  $\phi$  and magnitude of the missing transverse energy (MET), forming together an input of shape (19, 3) where MET  $\eta$  values are zero-padded by construction ( $\eta$  is zero for transverse quantities). For events with fewer than the maximum number of muons, electrons or jets, the input is also zero-padded, as commonly done in the L1T algorithm logic.

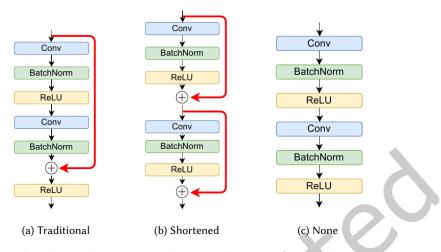

In order to account for resource consumption and latency of the data pre-processing step, we use a batch normalization layer<sup>63</sup> as the first layer for each model. For both architectures, CNN and DNN, we consider both a plain AE and a VAE. In the AE, the encoder provides directly the coordinates of the given input, projected in the latent space. In the VAE, the encoder returns the mean values  $\vec{\mu}$  and the standard deviation  $\vec{\sigma}$  of the *N*-dimensional Gaussian distribution that represents the latent-space probability density function associated with a given event.

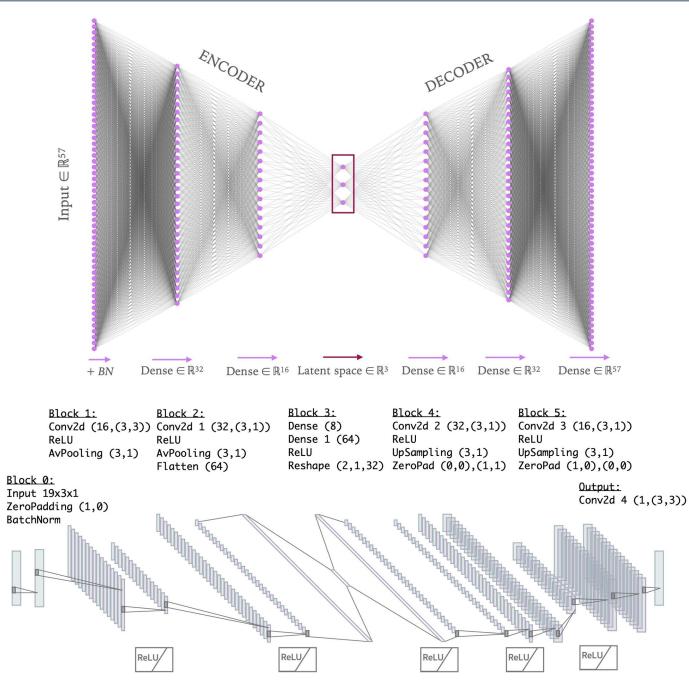

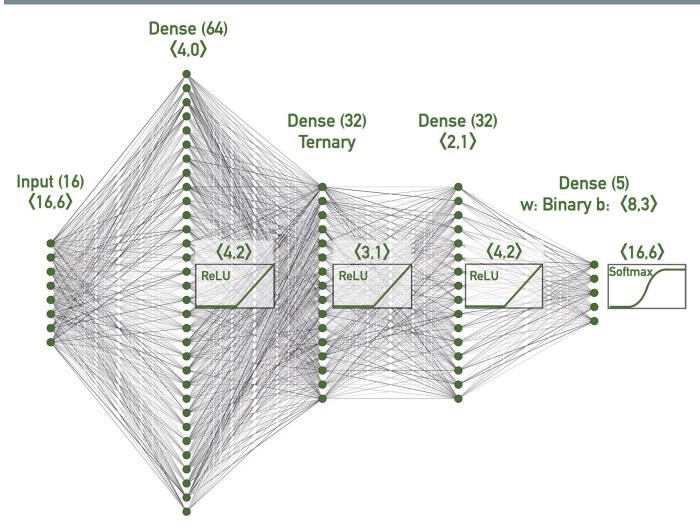

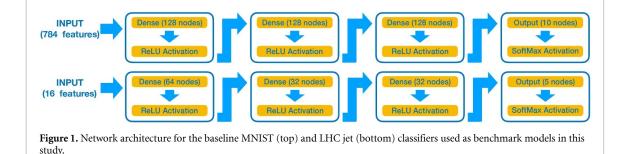

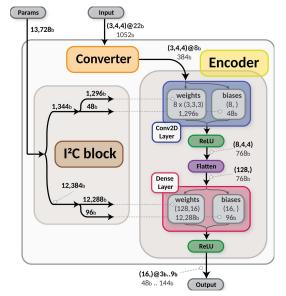

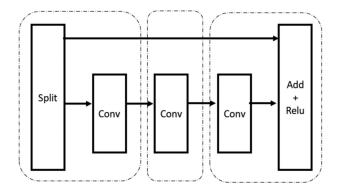

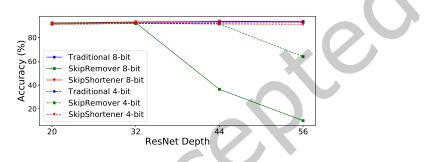

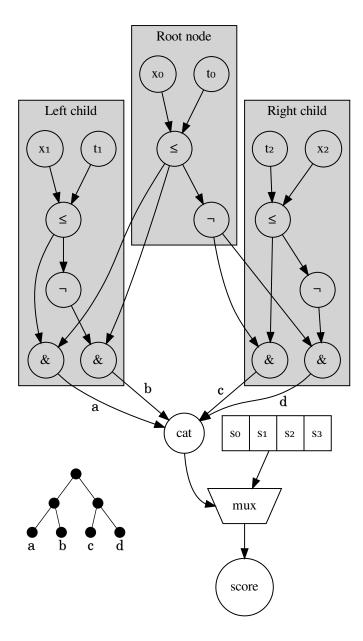

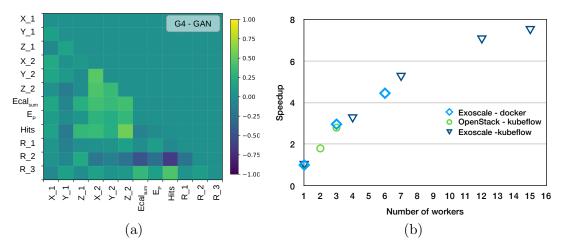

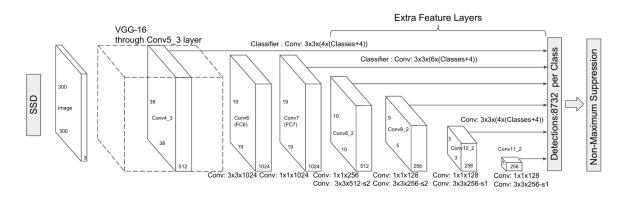

For the DNN model (shown on the top plot in Extended Data Fig. 1), all of the inputs are batch-normalized and passed through a stack of three fully connected layers, with 32, 16 and 3 nodes. The output of each layer is followed by a batch normalization layer and activated by a leaky ReLU function<sup>64</sup>. The decoder consists of a stack of three layers, with 16, 32 and 57 nodes. As for the encoder, we use a batch normalization layer between the fully connected layer and its activation. The last layer has no activation function, while leaky ReLU is used for the others.

The CNN AE architecture is shown on the bottom plot in Extended Data Fig. 1. The encoder takes as input the single-channel 2D array of three-vector including the two MET-related features

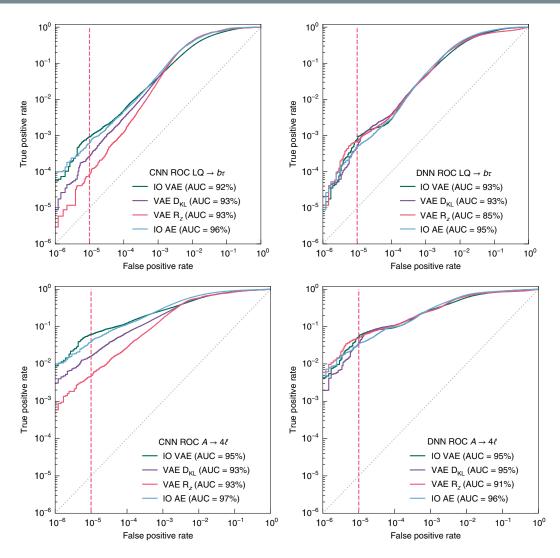

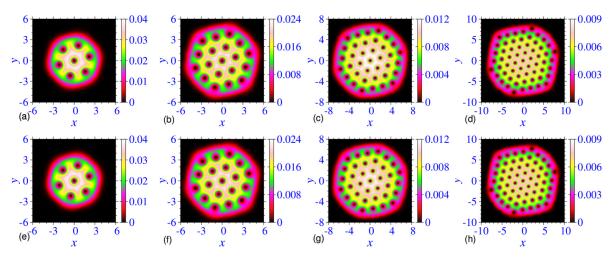

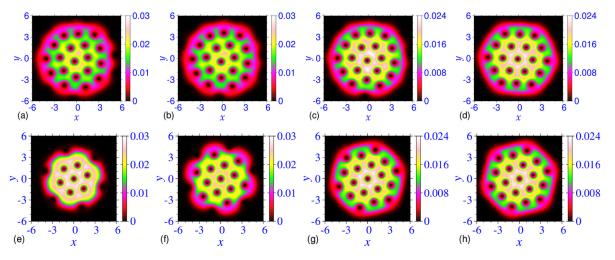

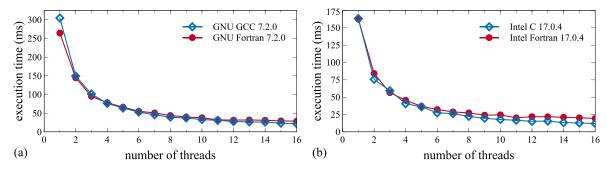

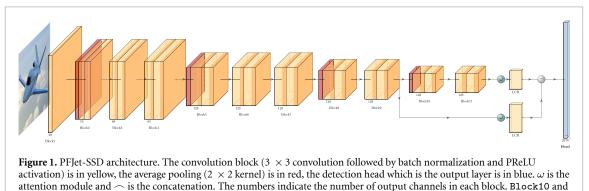

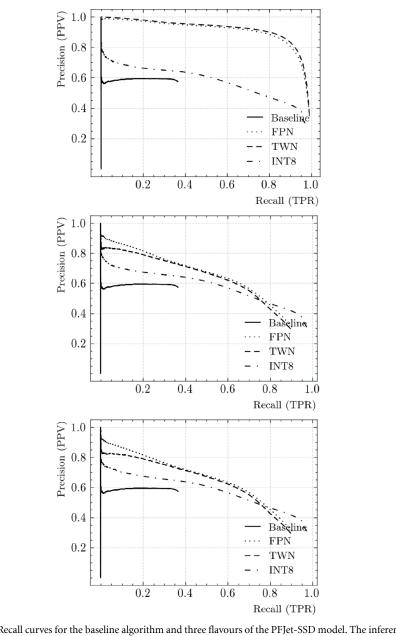

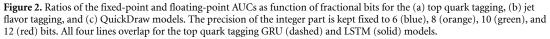

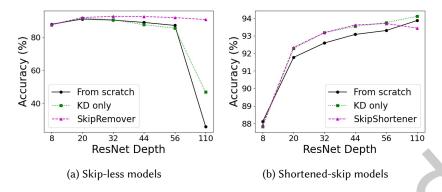

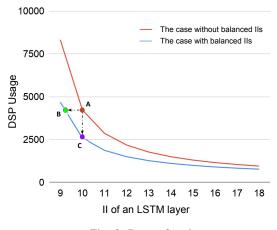

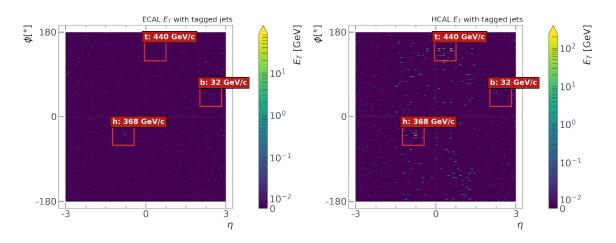

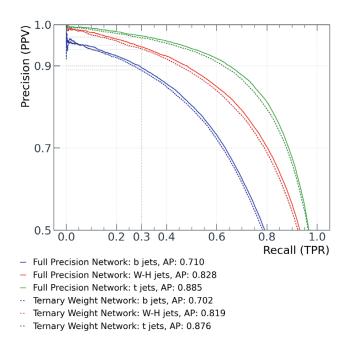

**Fig. 1** Model performance at floating-point precision. ROC curves of four AD scores (IO AD for AE and VAE models,  $R_z$  and  $D_{KL}$  ADs for the VAE models) for the CNN (left) and DNN (right) models, obtained from the two new physics benchmark models:  $LQ \rightarrow b\tau$  (top) and  $A \rightarrow 4\ell$  (bottom).

(magnitude and  $\phi$  angle) and zeros for MET  $\eta$ , resulting in a total input size of  $19 \times 3 \times 1$ . It should be emphasized that we are not using image data, rather treating tabular data as a 2D image to make it possible to explore CNN architectures. The input is scaled by a batch normalization layer and then processed by a stack of two CNN blocks, each including a 2D convolutional layer followed by a ReLU<sup>65</sup> activation function. The first layer has 16 3 × 3 kernels, without padding to ensure that  $p_{\rm T}$ ,  $\eta$  and  $\phi$  inputs do not share weights. The second layer has 32 3×1 kernels. Both layers have no bias parameters and a stride set to one. The output of the second CNN block is flattened and passed to a DNN layer, with eight neurons and no activation, which represents the latent space. The decoder takes this as input to a dense layer with 64 nodes and ReLU activation, and reshapes it into a  $2 \times 1 \times 32$  table. The following architecture mirrors the encoder architecture with two CNN blocks with the same number of filters as in the encoder and with ReLU activation. Both are followed by an upsampling layer, in order to mimic the result of a transposed convolutional layer. Finally, one convolutional layer with a single filter and no activation function is added. Its output is interpreted as the AE-reconstructed input.

The CNN and DNN VAEs are derived from the AEs, including the  $\overrightarrow{\mu}$  and  $\overrightarrow{\sigma}$  Gaussian sampling in the latent space.

All models are implemented in TENSORFLOW, and trained on the background dataset by minimizing a customized mean squared error (MSE) loss with the Adam<sup>66</sup> optimizer. In order to aid the network learning process, we use a dataset with standardized  $p_{\rm T}$  as a target, so that all the quantities are  $\mathcal{O}(1)$ . To account for physical boundaries of  $\eta$  and  $\phi$ , for those features a re-scaled tanh activation is used in the loss computation. In addition, the sum in the MSE loss is modified in order to ignore the zero-padding entries of the input dataset and the corresponding outputs. When training the VAE, the loss is changed to:

$$\mathcal{L} = (1 - \beta) \text{MSE}(\text{Output, Input}) + \beta D_{\text{KL}}(\overrightarrow{\mu}, \overrightarrow{\sigma}), \qquad (1)$$

where MSE labels the reconstruction loss (also used in the AE training),  $D_{\rm KL}$  is the Kullback–Leibler regularization term  $^{67}$  usually adopted for VAEs

$$D_{KL}(\overrightarrow{\mu}, \overrightarrow{\sigma}) = -\frac{1}{2} \sum_{i} \left( \log\left(\sigma_{i}^{2}\right) - \sigma_{i}^{2} - \mu_{i}^{2} + 1 \right), \qquad (2)$$

and  $\beta$  is a hyperparameter defined in the range  $[0, 1]^{68}$ .

Both models are trained for 100 epochs with a batch size of 1,024, using early stopping if there is no improvement in the loss observed after ten epochs. All models are trained with floating point precision on an NVIDIA RTX2080 GPU. We refer to these as the baseline floating-point (BF) models.

## ARTICLES

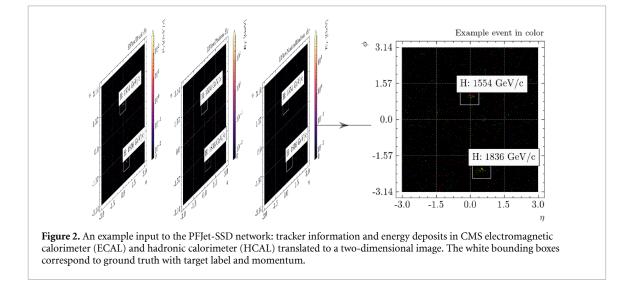

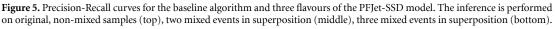

**Fig. 2** | Model performance at floating-point precision. ROC curves of four AD scores (IO AD for AE and VAE models,  $R_z$  and  $D_{KL}$  ADs for the VAE models) for the CNN (left) and DNN (right) models, obtained from two new physics benchmark models:  $h^{\pm} \rightarrow \tau \nu$  (top) and  $h^0 \rightarrow \tau \tau$  (bottom).

#### Anomaly detection scores

An autoencoder is optimized to retain the minimal set of information needed to reconstruct an accurate estimate of the input. During inference, an autoencoder might have problems generalizing to topologies it was not exposed to during training. Selecting events where the autoencoder output is far from the given input is often seen as an effective AD algorithm. The simplest solution is to use the same metric that defines the training loss function. In our case, we use the modified MSE between the input and the output. We refer to this strategy as input–output (IO) AD.

In the case of a VAE deployed in the L1T, one cannot simply exploit an IO AD strategy since this would require sampling random numbers on the FPGA. One could generate pseudo-random numbers exploiting meta information (for example, the event number) or symmetries in data (for example, the  $\phi$  coordinate of one of the objects). This might imply a limitation on the dimensionality of the latent space, which might impact performance. Moreover, one would have to store random numbers on the FPGA, which would consume resources and increase the latency. We did not explore this possibility further. Instead, we consider an alternative strategy by defining an AD score based on the  $\overrightarrow{\mu}$  and  $\overrightarrow{\sigma}$  values returned by the encoder (see equation (1)). In particular, we consider two options: the KL divergence term entering the VAE loss (see equation (2)) and the *z*-score of the origin  $\overrightarrow{0}$  in the latent space with respect to a Gaussian distribution centred at  $\overrightarrow{\mu}$  with standard deviation  $\overrightarrow{\sigma}$  (ref. <sup>10</sup>):

$$R_z = \sum_i \frac{\mu_i^2}{\sigma_i^2}.$$

(3)

These two AD scores have several benefits we take advantage of: Gaussian sampling is avoided; we save significant resources and latency by not evaluating the decoder; and we do not need to buffer the input data for computation of the MSE. During the model optimization, we tune  $\beta$  so that we obtain (on the benchmark signal models) comparable performance for the D<sub>KL</sub> AD score and the IO AD score of the VAE. In practice, one should train the model using real data, which might contain a very small fraction of signal. Previous studies have verified<sup>16</sup> that small rates of signal contamination have little effect on the training. One would use simulated signals in the same manner as in this paper to tune model parameters. Such a procedure would not bias the architecture choice towards specific signals, given the low dependence of the optimal  $\beta$  value on the nature of the anomaly.

#### Performance at floating-point precision

The model performance is assessed using the four new physics benchmark signals. The anomaly-detection scores considered in

| Model   | AD score        |                        | TPR @                 | 0 FPR 10⁻⁵ (%)                 |                               |                        |                       | AUC (%)                        |                               |

|---------|-----------------|------------------------|-----------------------|--------------------------------|-------------------------------|------------------------|-----------------------|--------------------------------|-------------------------------|

|         |                 | $LQ \rightarrow b\tau$ | $A \rightarrow 4\ell$ | $h^{\pm} \rightarrow \tau \nu$ | $h^{ m o}  ightarrow 	au 	au$ | $LQ \rightarrow b\tau$ | $A \to 4 \mathscr{C}$ | $h^{\pm} \rightarrow \tau \nu$ | $h^{ m o}  ightarrow 	au 	au$ |

| CNN VAE | 10              | 0.09                   | 6.19                  | 0.10                           | 0.11                          | 92                     | 95                    | 95                             | 85                            |

|         | D <sub>KL</sub> | 0.03                   | 1.63                  | 0.08                           | 0.09                          | 93                     | 93                    | 93                             | 82                            |

|         | R <sub>z</sub>  | 0.01                   | 0.48                  | 0.04                           | 0.04                          | 93                     | 93                    | 93                             | 82                            |

| CNN AE  | 10              | 0.06                   | 3.89                  | 0.08                           | 0.09                          | 96                     | 97                    | 96                             | 88                            |

| DNN VAE | Ю               | 0.08                   | 5.33                  | 0.08                           | 0.10                          | 93                     | 95                    | 95                             | 85                            |

|         | D <sub>KL</sub> | 0.05                   | 3.78                  | 0.08                           | 0.10                          | 93                     | 95                    | 94                             | 84                            |

|         | R <sub>z</sub>  | 0.07                   | 4.90                  | 0.07                           | 0.10                          | 85                     | 91                    | 87                             | 74                            |

| DNN AE  | 10              | 0.05                   | 3.47                  | 0.06                           | 0.09                          | 95                     | 96                    | 96                             | 88                            |

Table 1 | Performance assessment of the CNN and DNN models, for different AD scores and different new physics benchmark scenarios

The best-performing autoencoder model for each anomaly is highlighted in bold.

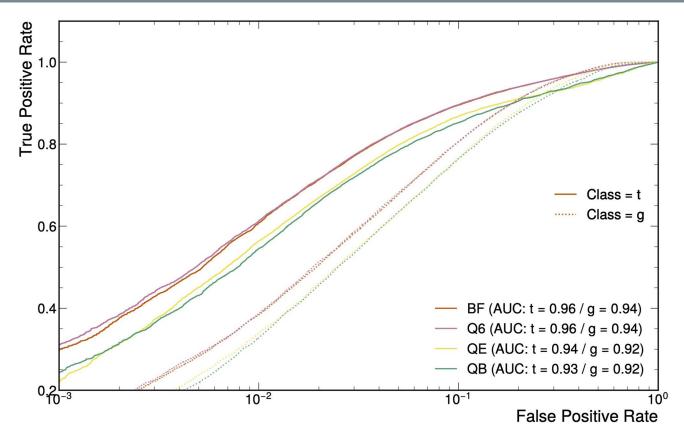

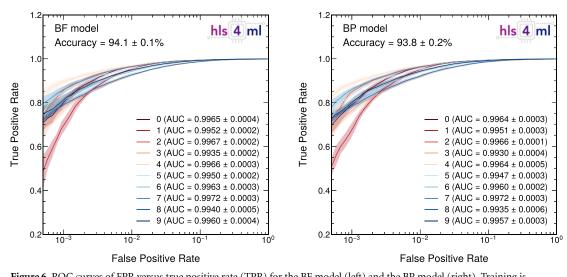

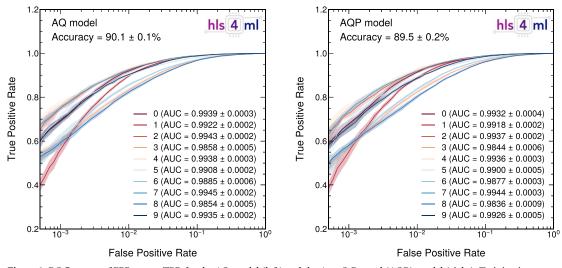

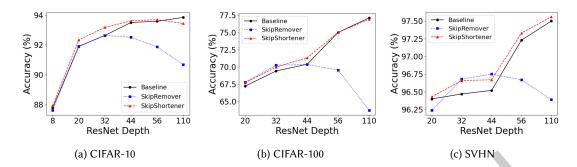

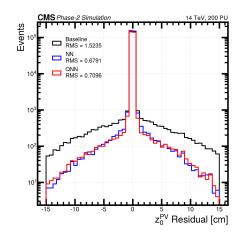

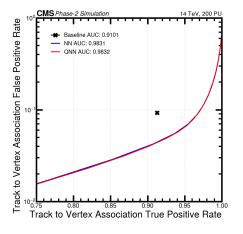

this paper are IO AD for the AE models,  $R_z$  and  $D_{KL}$  ADs for the VAE models. For completeness, results obtained from the IO AD score of the VAE models are also shown. The receiver operating characteristic (ROC) curves in Figs. 1 and 2 show the true positive rate (TPR) as a function of the false positive rate (FPR), computed by changing the lower threshold applied on the different anomaly scores. We further quantify the AD performance quoting the area under the ROC curve (AUC) and the TPR corresponding to an FPR working point of  $10^{-5}$  (see Table 1), which on this dataset corresponds to the reduction of the background rate to approximately 1,000 events per month.

Even if the VAE- $D_{KL}$  TPR is smaller than the corresponding full-precision model for certain benchmark signals, the TPR values are similar after pruning. So, we conclude that  $D_{KL}$  can be used as an anomaly metric for the rest of this work. The  $R_2$  metric performs worse and is therefore not included in the following studies.

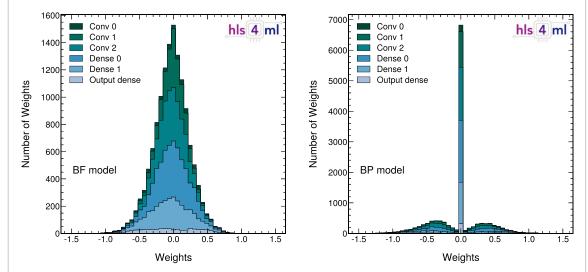

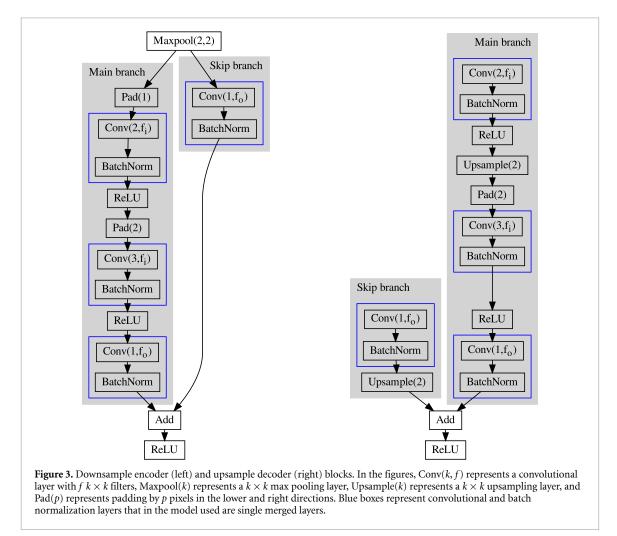

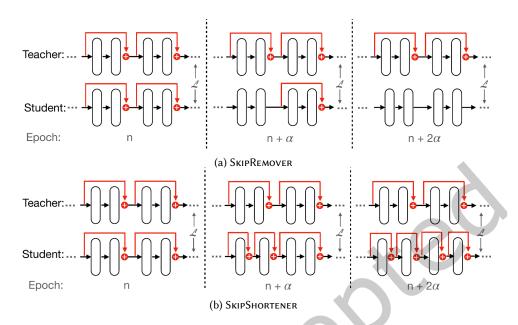

#### Model compression

We compress the BF model by pruning the dense and convolutional layers by 50% of their connections, following the a previously reported procedure28. Pruning is enforced using the polynomial decay implemented in TENSORFLOW pruning API, a KERAS-based<sup>69</sup> interface consisting of a simple drop-in replacement of KERAS layers. A sparsity of 50% is targeted, meaning only 50% of the weights are retained in the pruned layers and the remaining ones are set to zero. The pruning is set to start from the fifth epoch of the training to ensure the model is closer to a stable minimum before removing weights deemed unimportant. By pruning the BF model layers to a target sparsity of 50%, the number of floating-point operations required when evaluating the model, can be significantly reduced. We refer to the resulting model as the baseline pruned (BP) model. For the VAE, only the encoder is pruned, since only that will be deployed on FPGA. The BP models are taken as a reference to evaluate the resource saving of the following compression strategies, including QAT and PTQ.

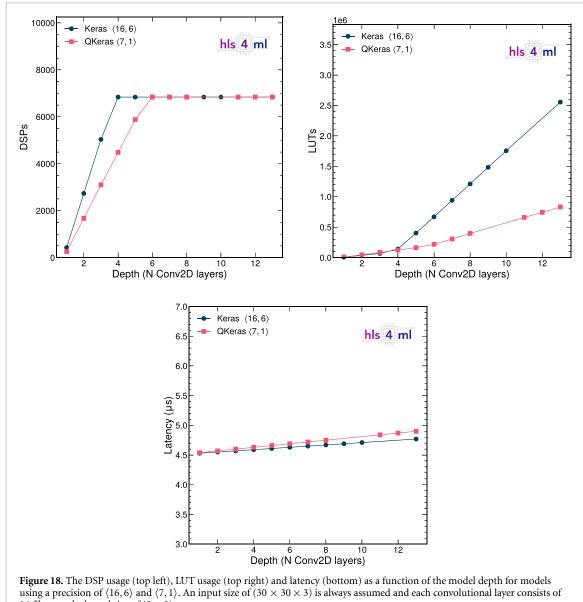

Furthermore, we perform a QAT of each model described in 'Autoencoder models', implementing them in the QKERAS library<sup>32</sup>. The bit precision is scanned between 2 and 16 with a 2-bit step. When quantizing a model, we also impose a pruning of the dense (convolutional) layers by 50%, as done for the DNN (CNN) BP models. The results of QAT are compared to results obtained by applying a fixed-point precision to a BP floating-point model (that is using PTQ), using the same bit precision scan.

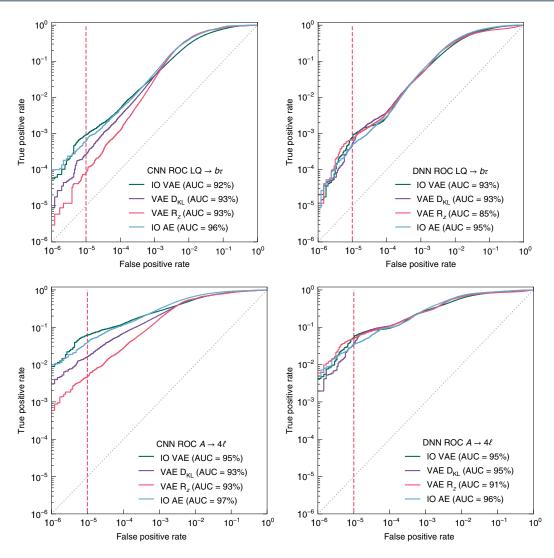

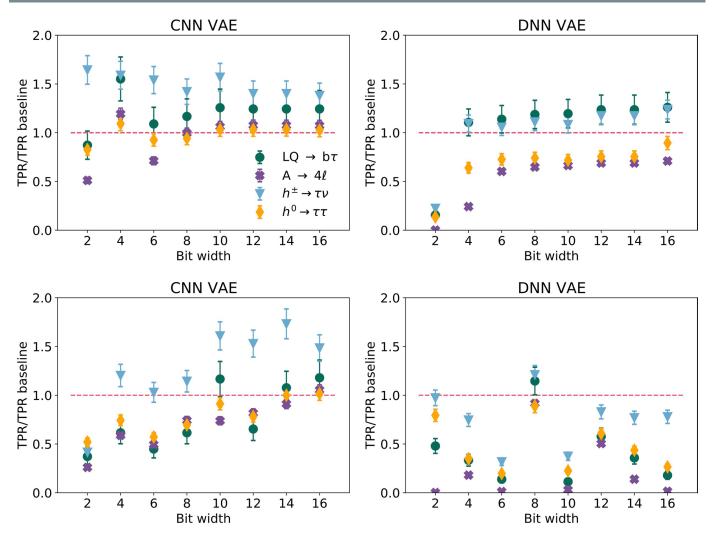

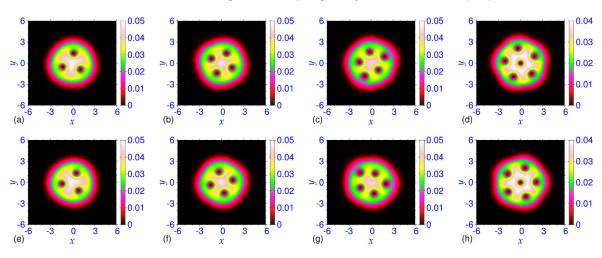

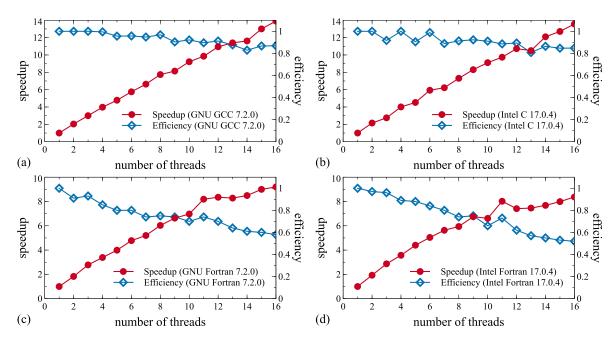

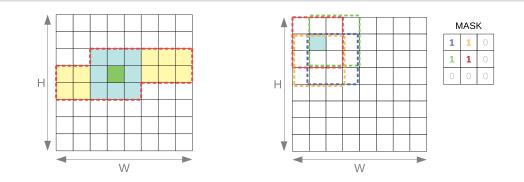

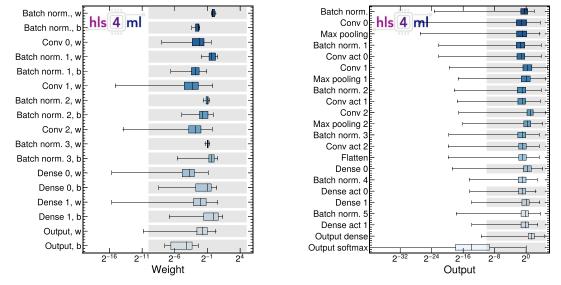

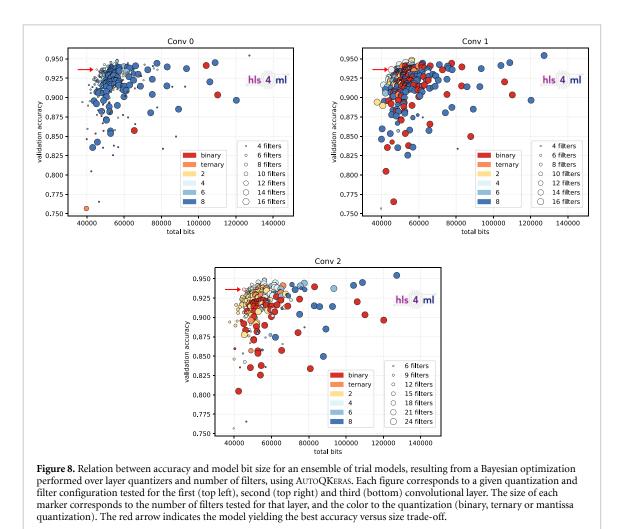

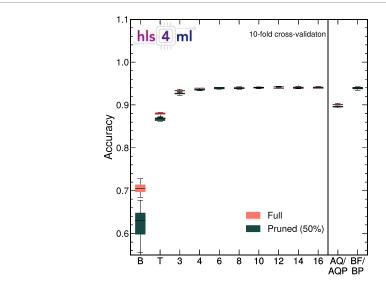

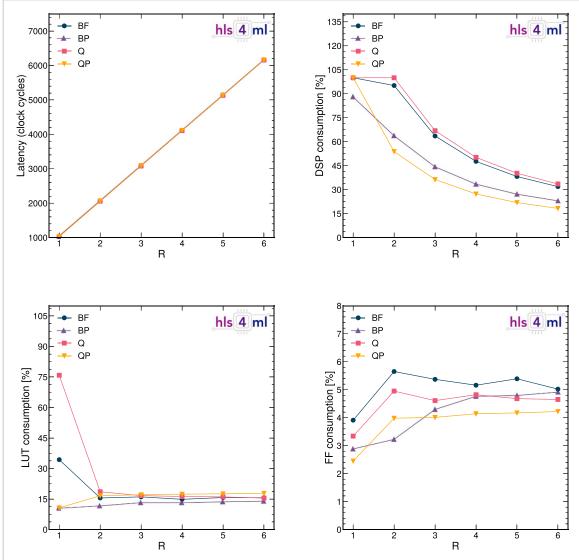

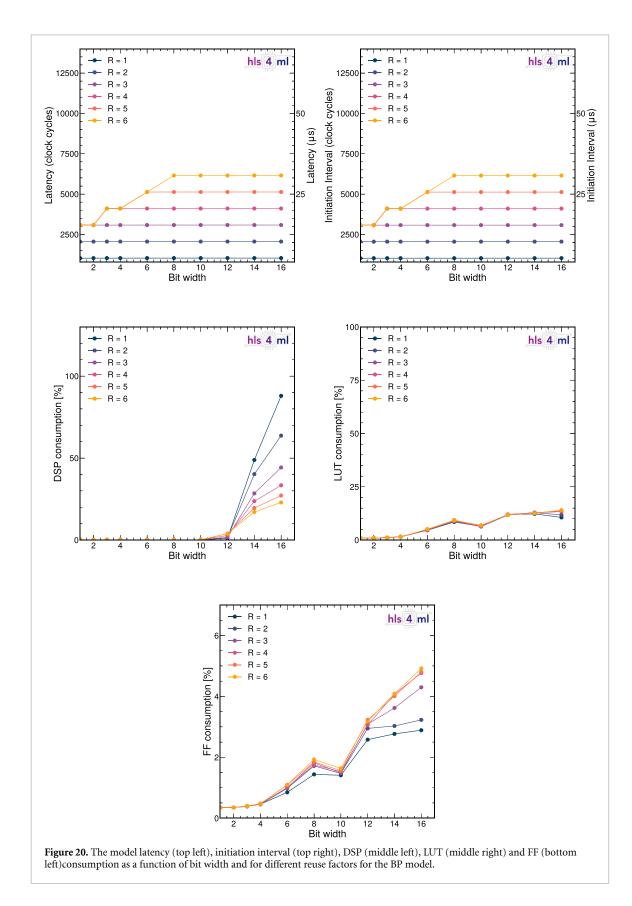

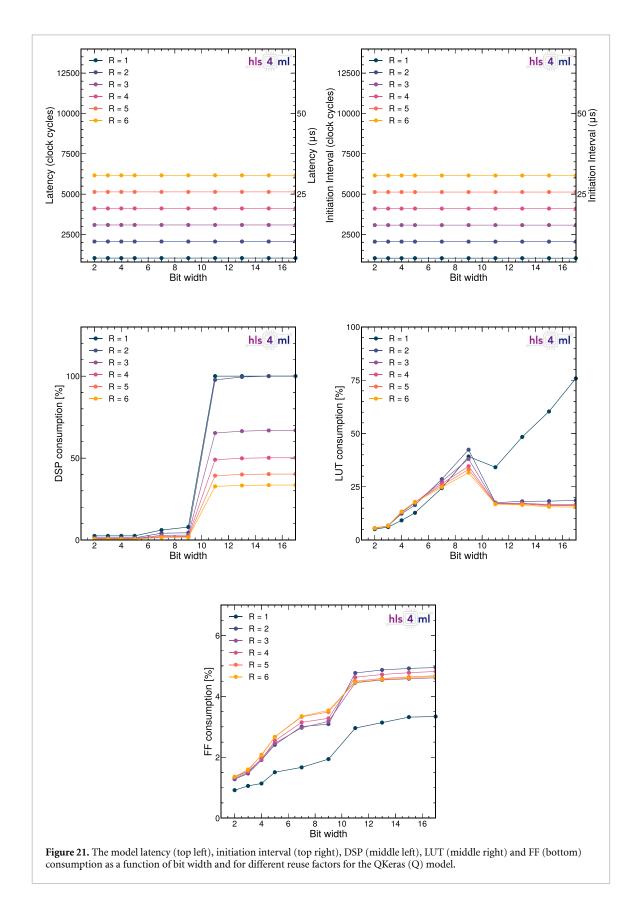

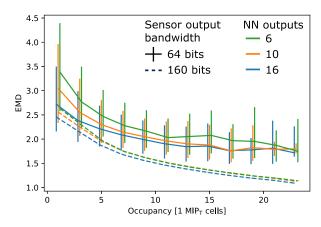

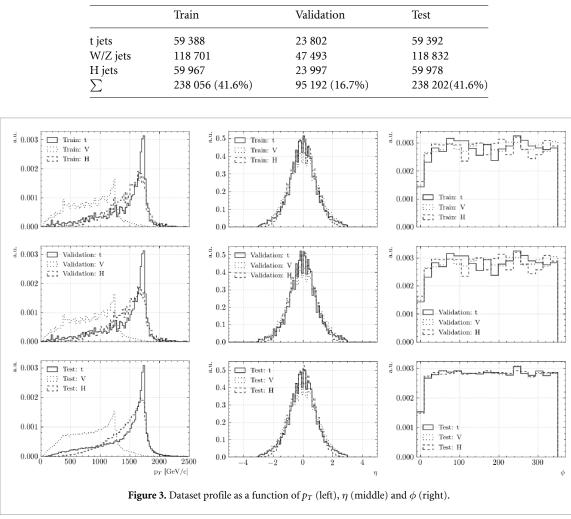

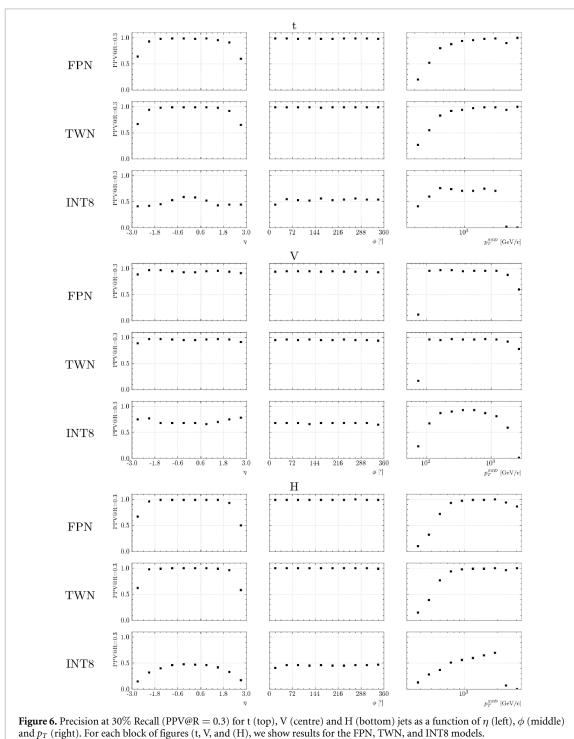

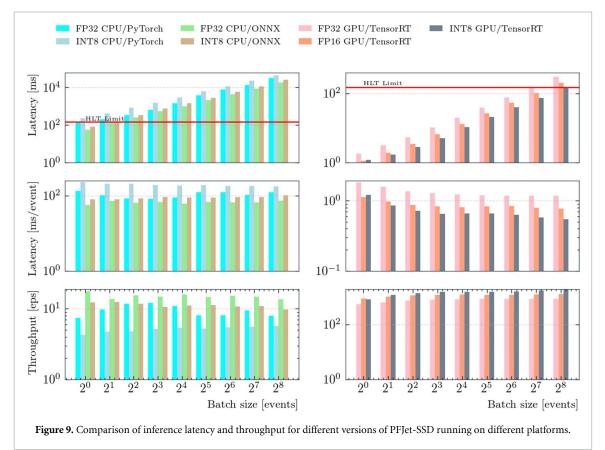

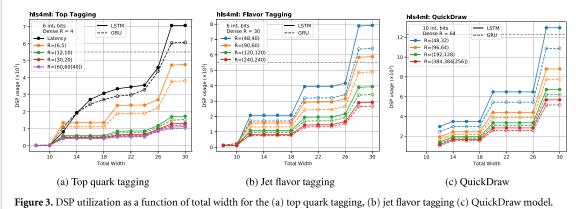

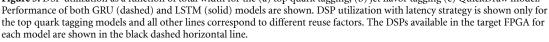

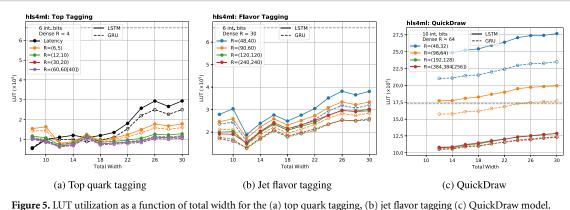

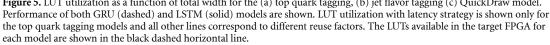

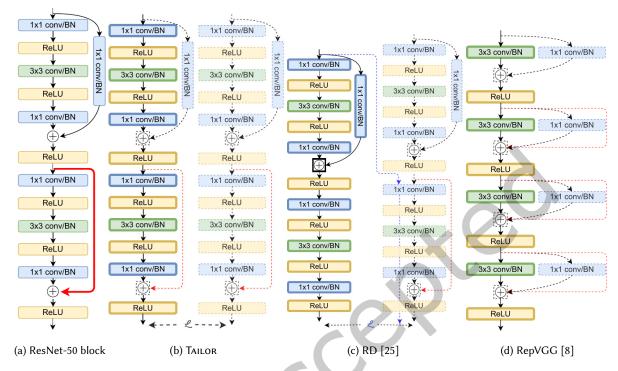

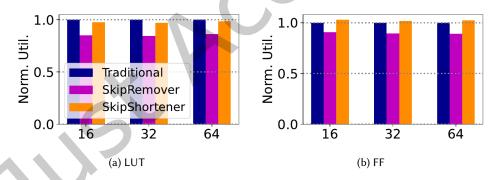

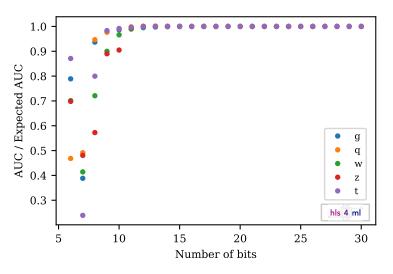

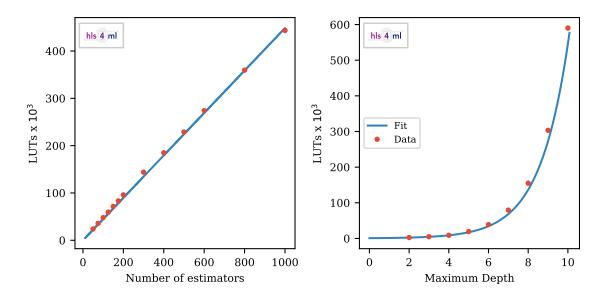

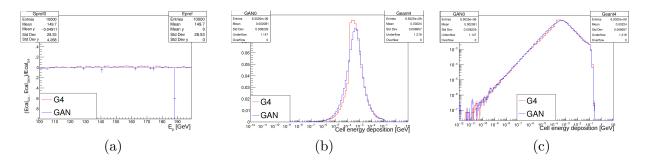

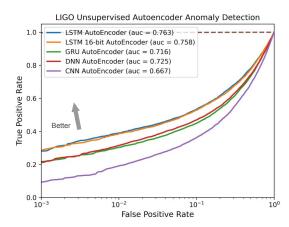

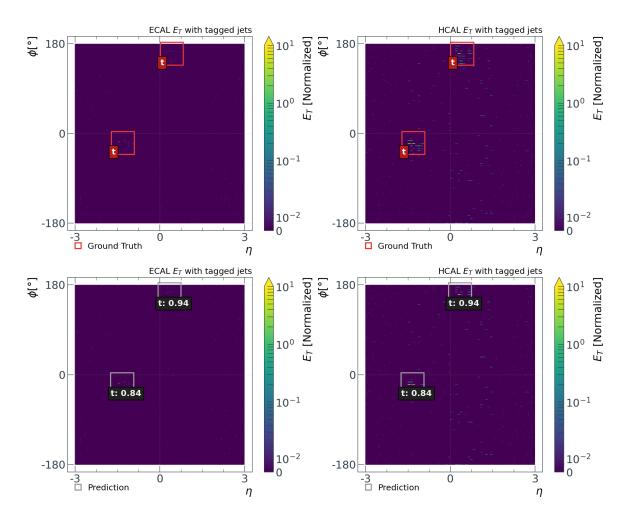

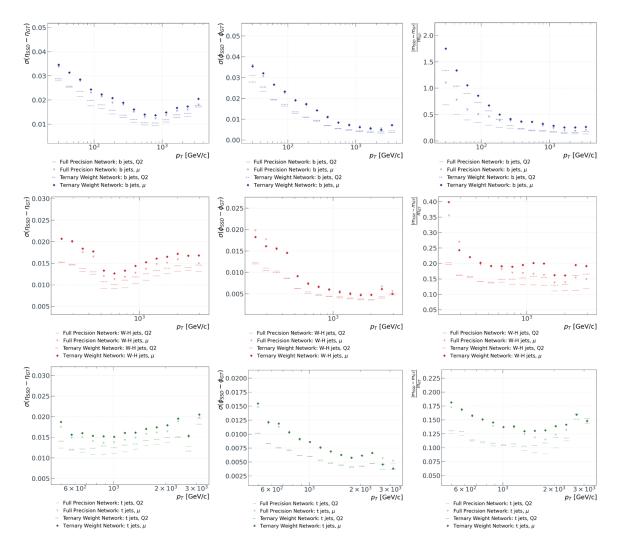

Performance of the quantized models, both for QAT and PTQ, is assessed using the TPR obtained for an FPR of  $10^{-5}$  for the given precision. The bottom plots in Fig. 3 and Extended Data Fig. 2 show ratios of QAT performance quantities obtained for each bit width

with respect to the BP model performance of the AE and VAE, respectively. The top plots show ratios of PTQ performance quantities obtained in the same manner as for QAT.

Based on these ratio plots, the precision used for the final model is chosen. The performance of the VAEs is not stable as a function of bit width, since the AD figure of merit used for inference ( $D_{KL}$ ) is different from those minimized during the QAT training (VAE IO +  $D_{KL}$ ). Therefore, we use PTQ compression for both DNN and CNN VAEs because they show stable results as a function of the bit width. For autoencoders, both quantization approaches show stable results, and therefore we choose quantization-aware training. For all the models a bit width of 8 is chosen, apart from the CNN VAE for which a bit width of 4 is found to be the best. The performance numbers for the chosen models are summarized in Table 2.

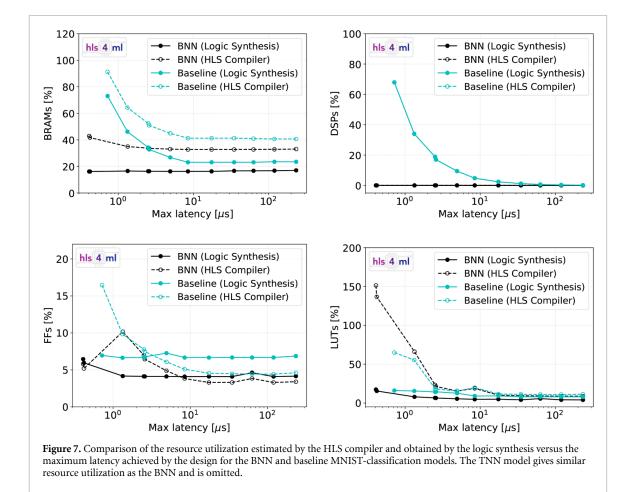

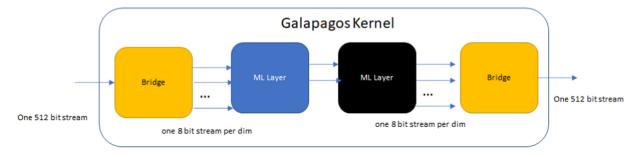

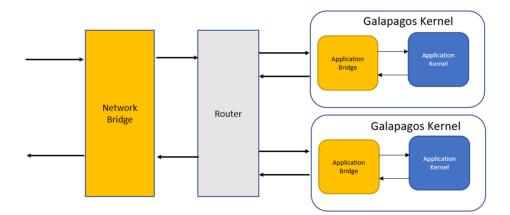

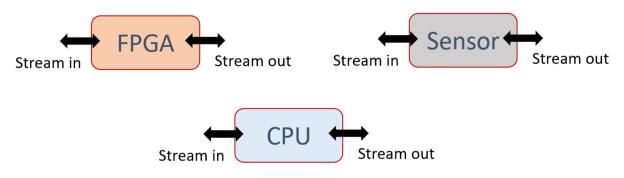

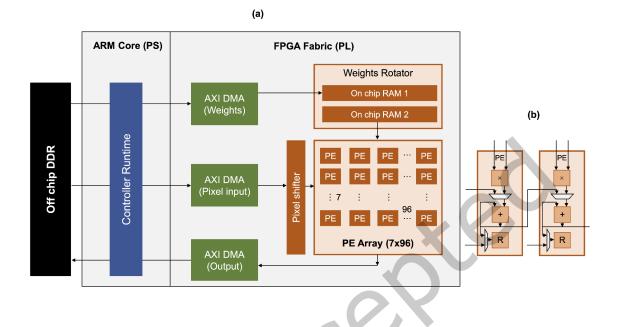

#### Porting the algorithm to FPGAs

The models described above are translated into firmware using hls4ml, then synthesized with Vivado HLS 2020.1<sup>70</sup>, targeting a Xilinx Virtex UltraScale+ VU9P (xcvu9p-flgb2104-2-e) FPGA with a clock frequency of 200 MHz. In order to have fair resource and latency estimations, obtained from the HLS C simulation we have implemented custom layers in hls4ml, which in the case of AE computes the loss function between the input and network output and for VAE computes the D<sub>KL</sub> term of the loss.

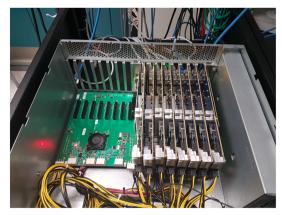

A summary of the accuracy, resource consumption, and latency for the QAT DNN and CNN BP AE models, and the PTQ DNN and CNN BP VAE models is shown in Table 3. We find the resources are less than about 12% of the available FPGA resources, except for the CNN AE, which uses up to 47% of the look-up tables (LUTs). Moreover, the latency is less than about 365ns for all models except the CNN AE, which has a latency of 1,480 ns. The II for all models is within the required 115ns, again except the CNN AE. Based on these, both types of architectures with both types of autoencoders are suitable for application at the LHC L1T, except for the CNN AE, which consumes too much of the resources.

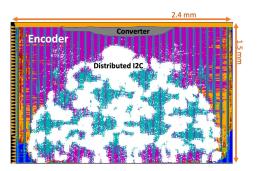

Since the performance of all the models under study are of a similar level, we choose the 'best' model based on the smallest resource consumption, which turns out to be DNN VAE. This model was integrated into the emp-fwk infrastructure firmware for LHC trigger boards<sup>71</sup>, targeting a Xilinx VCU118 development kit, with the same VU9P FPGA as previously discussed. Data were loaded into onboard buffers mimicking the manner in which data arrives from optical fibres in the L1T system. The design was operated at 240 MHz, and the model predictions observed at the output were consistent with those captured from the HLS C simulation. For this model we also provide resource and latency estimates for a Xilinx Virtex 7 690 FPGA, which is the FPGA most widely used in the current CMS trigger.

**Fig. 3 | Compressed model performance.** TPR ratios versus model bit width for the AE CNN (left) and DNN (right) models tested on four new physics benchmark models, using mean squared error as figure of merit for PTQ (top) and QAT (bottom) strategies.

Table 2 | Performance assessment of the quantized and pruned CNN and DNN models, for different AD scores and different new physics benchmark scenarios

| Model              | AD score        | TPR @ FPR 10 <sup>-5</sup> [%] |                                        |                                |                               | Α                      | UC[%]                                  |                                |                                   |

|--------------------|-----------------|--------------------------------|----------------------------------------|--------------------------------|-------------------------------|------------------------|----------------------------------------|--------------------------------|-----------------------------------|

|                    |                 | $LQ \rightarrow b\tau$         | $A \mathop{\rightarrow} 4 \mathscr{C}$ | $h^{\pm} \rightarrow \tau \nu$ | $h^{ m o}  ightarrow 	au 	au$ | $LQ \rightarrow b\tau$ | $A \mathop{\rightarrow} 4 \mathscr{C}$ | $h^{\pm} \rightarrow \tau \nu$ | $h^{\rm o} \rightarrow \tau \tau$ |

| CNN AE QAT 4 bits  | 10              | 0.09                           | 5.96                                   | 0.10                           | 0.13                          | 94                     | 96                                     | 96                             | 88                                |

| CNN VAE PTQ 8 bits | D <sub>KL</sub> | 0.05                           | 2.56                                   | 0.06                           | 0.12                          | 84                     | 84                                     | 85                             | 71                                |

| DNN AE QAT 8 bits  | IO              | 0.08                           | 5.48                                   | 0.09                           | 0.11                          | 95                     | 96                                     | 96                             | 88                                |

| DNN VAE PTQ 8 bits | D <sub>KL</sub> | 0.08                           | 3.41                                   | 0.09                           | 0.08                          | 92                     | 94                                     | 94                             | 81                                |

#### Conclusions

We discussed how to extend new physics detection strategies at the LHC with autoencoders deployed in the L1T infrastructure of the experiments. In particular, we show how one could deploy a deep neural network or convolutional neural network AE on a FPGA using the hls4ml library, within a  $\mathcal{O}(1)\mu$ s latency and with small resource utilization once the model is quantized and pruned. We show that one can retain accuracy by compressing the model at training time. Moreover, we discuss different strategies to identify potential anomalies. We show that one could perform the AD with a VAE using the projected representation of a given input in the latent space, which has several advantages for an FPGA implementation: (1) no need to sample Gaussian-distributed pseudorandom numbers (preserving the deterministic outcome of the trigger decision) and (2) no need to run the decoder in the trigger, resulting in a significant resource saving.

The DNN (V)AE models use less than 5% of the Xilinx VU9P resources and the corresponding latency is within 130ns, while the CNN VAE uses less than 12% and the corresponding latency is 365ns. All three models have the initiation interval within the strict limit imposed by the frequency of bunch crossing at the LHC. With this work, we have identified and finalized the necessary ingredients

to deploy (V)AEs in the L1T of the LHC experiments for Run 3 to accelerate the search for unexpected signatures of new physics.

The aim is to use these algorithms in the trigger in order to create a catalogue of anomalous events that researchers could explore, for example, with clustering techniques. Furthermore, one could perform traditional data analysis, provided a (non-trivial) understanding of the effect of the trigger selection on the kinematic distribution. In presence of a good description of the loss distribution, the approach used in ref.<sup>72</sup> could be adopted.

#### Data availability

The data used in this study are openly available at Zenodo<sup>57-60,62</sup>.

#### Code availability

The QKeras library is available at github.com/google/qkeras, where the work presented here is using QKeras version 0.9.0. The hls4ml library with custom layers used in the paper are under AE\_L1\_paper branch and available at https://github.com/fastmachinelearning/ hls4ml/tree/AE\_L1\_paper.

Received: 12 August 2021; Accepted: 6 January 2022; Published online: 23 February 2022

## NATURE MACHINE INTELLIGENCE

| Table 3   Resource utilization and | atency for the quantized and | pruned DNN and CNN (V)AE models |

|------------------------------------|------------------------------|---------------------------------|

|------------------------------------|------------------------------|---------------------------------|

| Model                           | Hardware      | DSP [%] | LUT [%] | FF [%] | BRAM [%] | Latency [ns] | ll [ns] |

|---------------------------------|---------------|---------|---------|--------|----------|--------------|---------|

| DNN AE QAT 8 bits               | Xilinx VU9P   | 2       | 5       | 1      | 0.5      | 130          | 5       |

| CNN AE QAT 4 bits               | Xilinx VU9P   | 8       | 47      | 5      | 6        | 1,480        | 895     |

| DNN VAE <sup>a</sup> PTQ 8 bits | Xilinx VU9P   | 1       | 3       | 0.5    | 0.3      | 80           | 5       |

| DNN VAE PTQ 8 bits              | Xilinx V7-690 | 3       | 9       | 3      | 0.4      | 205          | 5       |

| CNN VAE PTQ 8 bits              | Xilinx VU9P   | 10      | 12      | 4      | 2        | 365          | 115     |

Resources are based on the Vivado estimates from Vivado HLS 2020.1 for a clock period of 5ns on Xilinx VU9P. \*For the DNN VAE model, resources estimation is also provided based on Xilinx V7-690

#### References

- 1. LHC Machine. JINST 3, S08001 (2008).

- Aad, G. et al. The ATLAS Experiment at the CERN Large Hadron Collider. J. Instrum. 3, S08003 (2008).

- Chatrchyan, S. et al. The CMS Experiment at the CERN LHC. J. Instrum. 3, S08004 (2008).

- 4. Sirunyan, A. M. et al. Performance of the CMS Level-1 trigger in proton-proton collisions at  $\sqrt{s} = 13$  TeV. J. Instrum. 15, P10017 (2020).

- The Phase-2 upgrade of the CMS Level-1 trigger. CMS Technical Design Report CERN-LHCC-2020-004 CMS-TDR-021 (2020).

- Aad, G. et al. Operation of the ATLAS trigger system in Run 2. J. Instrum. 15, P10004 (2020).

- Technical Design Report for the Phase-II Upgrade of the ATLAS TDAQ System. ATLAS Technical Design Report CERN-LHCC-2017-020 ATLAS-TDR-029 (2017).

- Aad, G. et al. Observation of a new particle in the search for the standard model Higgs boson with the ATLAS detector at the LHC. *Phys. Lett. B* 716, 1 (2012).

- 9. Chatrchyan, S. et al. Observation of a new boson at a mass of 125 GeV with the CMS experiment at the LHC. *Phys. Lett. B* **716**, 30 (2012).

- 10. Aarrestad, T. et al. The dark machines anomaly score challenge: Benchmark data and model independent event classification for the large hadron collider. *SciPost Phys.* **12**, 2542 (2022).

- Kasieczka, G. et al. The LHC olympics 2020: A community challenge for anomaly detection in high energy physics. *Rep. Prog. Phys.* 84, 124201 (2021).

- Kingma, D. P. & Welling, M. Auto-encoding variational Bayes. Preprint at https://arxiv.org/abs/1312.6114 (2014).

Reserve D. D. Geberger, D. Geberger, D. Geberger, and D. J. Schwarz, D. S. Schwarz, D. Schwarz, Schwarz, D. Schwarz, Schwarz, D. Schwarz, Schwarz, Schwarz, D. Schwarz, Sc

- Rezende, D. J., Mohamed, S. & Wierstra, D. Stochastic backpropagation and approximate inference in deep generative models. Preprint at https://arxiv. org/abs/1401.4082 (2014).

- Heimel, T., Kasieczka, G., Plehn, T. & Thompson, J. M. QCD or What? SciPost Phys. 6, 30 (2019).

- 15. Farina, M., Nakai, Y. & Shih, D. Searching for new physics with deep autoencoders. *Phys. Rev. D* 101, 075021 (2020).

- Cerri, O. et al. Variational autoencoders for new physics mining at the Large Hadron Collider. J. High Eenergy Phys. 2019, 36 (2019).

- Knapp, O. et al. Adversarially Learned Anomaly Detection on CMS Open Data: re-discovering the top quark. *Eur. Phys. J. Plus* 136, 236 (2021).

- Venieris, S. I., Kouris, A. & Bouganis, C.-S. Toolflows for mapping convolutional neural networks on FPGAs: A survey and future directions. Preprint at https://arxiv.org/abs/1803.05900 (2018).

- Guo, K., Zeng, S., Yu, J., Wang, Y. & Yang, H. A survey of FPGA-based neural network inference accelerators. https://arxiv.org/abs/1712.08934 (2019).

- Shawahna, A., Sait, S. M. & El-Maleh, A. FPGA-based accelerators of deep learning networks for learning and classification: a review. *IEEE Access* 7, 7823 (2019).

- Umuroglu, Y. et al. FINN: A framework for fast, scalable binarized neural network inference. In Proc. 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays 65 (ACM, 2017).

- Blott, M. et al. FINN-R: An end-to-end deep-learning framework for fast exploration of quantized neural networks. Preprint at https://arxiv.org/ abs/1809.04570 (2018).

- 23. Summers, S. et al. Fast inference of boosted decision trees in FPGAs for particle physics. J. Instrum. 15, P05026 (2020).

- Hong, T. M. et al. Nanosecond machine learning event classification with boosted decision trees in FPGA for high energy physics. *J. Instrum.* 16, P08016 (2021).

- Duarte, J. et al. Fast inference of deep neural networks in FPGAs for particle physics. J. Instrum. 13, P07027 (2018).

- Ngadiuba, J. et al. Compressing deep neural networks on FPGAs to binary and ternary precision with HLS4ML. *Mach. Learn. Sci. Technol.* 2, 2632 (2020).

- Iiyama, Y. et al. Distance-weighted graph neural networks on FPGAs for real-time particle reconstruction in high energy physics. *Front. Big Data* 3, 598927 (2020).

- Aarrestad, T. et al. Fast convolutional neural networks on FPGAs with HLS4ML. Mach. Learn. Sci. Technol. 2, 045015 (2021).

- Heintz, A. et al. Accelerated charged particle tracking with graph neural networks on FPGAs. In 34th Conference on Neural Information Processing Systems (2020).

- Summers, S. et al. Fast inference of boosted decision trees in FPGAs for particle physics. J. Instrum. 15, P05026 (2020).

- 31. Coelho, C. Qkeras https://github.com/google/qkeras (2019).

- Coelho, C. N. et al. Automatic heterogeneous quantization of deep neural networks for low-latency inference on the edge for particle detectors. *Nat. Mach. Intell.* 3, 675–686 (2021).

- D'Agnolo, R. T. & Wulzer, A. Learning new physics from a machine. *Phys. Rev. D* 99, 015014 (2019).

- Mikuni, V., Nachman, B. & Shih, D. Online-compatible unsupervised non-resonant anomaly detection. Preprint at https://arxiv.org/abs/2111.06417 (2021).

- LeCun, Y., Denker, J. S. & Solla, S. A. Optimal brain damage. In Advances in Neural Information Processing Systems (ed. Touretzky, D. S.) Vol. 2, 598 (Morgan-Kaufmann, 1990).

- 36. Han, S., Mao, H. & Dally, W. J. Deep compression: compressing deep neural networks with pruning, trained quantization and Huffman coding. In 4th Int. Conf. Learning Representations (ed. Bengio, Y. & LeCun, Y.) (2016).

- Blalock, D., Ortiz, J. J. G., Frankle, J. & Guttag, J. What is the state of neural network pruning? In *Proc. Machine Learning and Systems* Vol. 2, 129 (2020).

- Moons, B., Goetschalckx, K., Berckelaer, N. V. & Verhelst, M. Minimum energy quantized neural networks. In 2017 51st Asilomar Conf. Signals, Systems, and Computers (ed. Matthews, M. B.) 1921 (2017).

- Courbariaux, M., Bengio, Y. & David, J.-P. BinaryConnect: Training deep neural networks with binary weights during propagations. In *Adv. Neural Information Processing Systems* (eds. Cortes, C., Lawrence, N. D., Lee, D. D., Sugiyama, M. & Garnett, R.) Vol. 28, 3123 (Curran Associates, 2015).

- Zhang, D., Yang, J., Ye, D. & Hua, G. LQ-nets: Learned quantization for highly accurate and compact deep neural networks. In *Proc. European Conference on Computer Vision* (eds. Ferrari, V., Hebert, M., Sminchisescu, C. & Weiss, Y.) (2018).

- Hubara, I., Courbariaux, M., Soudry, D., El-Yaniv, R. & Bengio, Y. Quantized neural networks: training neural networks with low precision weights and activations. *J. Mach. Learn. Res.* 18, 6869–6898 (2018).

- 42. Rastegari, M., Ordonez, V., Redmon, J. & Farhadi, A. XNOR-Net: ImageNet classification using binary convolutional neural networks. In *14th European Conf. Computer Vision* 525 (Springer, 2016).

- 43. Micikevicius, P. et al. Mixed precision training. In 6th Int. Conf. Learning Representations (2018).

- 44. Zhuang, B., Shen, C., Tan, M., Liu, L. & Reid, I. Towards effective low-bitwidth convolutional neural networks. In 2018 IEEE/CVF Conf. Computer Vision and Pattern Recognition 7920 (2018).

- 45. Wang, N., Choi, J., Brand, D., Chen, C.-Y. & Gopalakrishnan, K. Training deep neural networks with 8-bit floating point numbers. In *Adv. Neural Information Processing Systems* (eds. Bengio, S. et al.) Vol. 31, 7675 (Curran Associates, 2018).

- An, J. & Cho, S. Variational autoencoder based anomaly detection using reconstruction probability. *Special Lecture IE* 2, 1–18 (2015).

- Nagel, M., van Baalen, M., Blankevoort, T. & Welling, M. Data-free quantization through weight equalization and bias correction. In 2019 IEEE/ CVF International Conf. Computer Vision 1325 (2019).

- Meller, E., Finkelstein, A., Almog, U. & Grobman, M. Same, same but different: Recovering neural network quantization error through weight factorization. In *Proc. 36th International Conf. Machine Learning* (eds. Chaudhuri, K. & Salakhutdinov, R.) Vol. 97, 4486 (PMLR, 2019).

- Zhao, R., Hu, Y., Dotzel, J., Sa, C. D. & Zhang, Z. Improving neural network quantization without retraining using outlier channel splitting. In *Proc. 36th Int. Conference on Machine Learning* (eds. Chaudhuri, K. & Salakhutdinov, R.) Vol. 97, 7543 (PMLR, 2019).

- Banner, R., Nahshan, Y., Hoffer, E. & Soudry, D. Post-training 4-bit quantization of convolution networks for rapid-deployment. In *Adv. Neural Information Processing Systems* (eds. Wallach, H. et al.) Vol. 32, 7950 (Curran Associates, 2019).

- 51. Pappalardo, A. brevitas https://github.com/Xilinx/brevitas (2020).

- Shin, S., Boo, Y. & Sung, W. Knowledge distillation for optimization of quantized deep neural networks. In 2020 IEEE Workshop on Signal Processing Systems (2020).

- 53. Polino, A., Pascanu, R. & Alistarh, D. Model compression via distillation and quantization. In *Int. Conf. Learning Representations* (2018).

- 54. Gao, M. et al. An embarrassingly simple approach for knowledge distillation. Preprint at https://arxiv.org/abs/1812.01819 (2019).

- Mishra, A. & Marr, D. Apprentice: using knowledge distillation techniques to improve low-precision network accuracy. In *Int. Conf. Learning Representations* (2018).

- Nguyen, T. Q. et al. Topology classification with deep learning to improve real-time event selection at the LHC. Comput. Softw. Big Sci. 3, 12 (2019).

- Govorkova, E. et al. Unsupervised new physics detection at 40 mhz: LQ→b τ signal benchmark dataset. Zenodo https://doi.org/10.5281/zenodo.5055454 (2021).

- 58. Govorkova, E. et al. Unsupervised new physics detection at 40 mhz: A→4 leptons signal benchmark dataset. Zenodo https://doi.org/10.5281/zenodo.5046446 (2021).

- Govorkova, E. et al. Unsupervised new physics detection at 40 mhz: h<sup>0</sup> → ττ signal benchmark dataset. Zenodo https://doi.org/10.5281/zenodo.5061633 (2021).

- Govorkova, E. et al. Unsupervised new physics detection at 40 mhz: h<sup>+</sup> → τν signal benchmark dataset. Zenodo https://doi.org/10.5281/zenodo.5061688 (2021).

- 61. Govorkova, E. et al. LHC physics dataset for unsupervised new physics detection at 40 MHz. Preprint at https://arxiv.org/abs/2107.02157 (2021).

- Govorkova, E. et al. Unsupervised new physics detection at 40 mhz: training dataset. Zenodo https://doi.org/10.5281/zenodo.5046389 (2021).

- 63. Ioffe, S. & Szegedy, C. Batch normalization: accelerating deep network training by reducing internal covariate shift. In *Proc. 32nd International Conference on Machine Learning* (eds. Bach, F. & Blei, D.) Vol. 37, 448 (PMLR, 2015).

- Maas, A. L., Hannun, A. Y. & Ng, A. Y. Rectifier nonlinearities improve neural network acoustic models. In *ICML Workshop on Deep Learning for Audio, Speech and Language Processing* (2013).

- Nair, V. & Hinton, G. E. Rectified linear units improve restricted boltzmann machines. In *ICML* (eds. Fürnkranz, J. & Joachims, T.) 807 (Omnipress, 2010).

- Kingma, D. P. & Ba, J. Adam: A Method for Stochastic Optimization. Preprint at https://arxiv.org/abs/1412.6980 (2014).

- 67. Joyce, J. M. in *International Encyclopedia of Statistical Science* 720–722 (Springer, 2011); https://doi.org/10.1007/978-3-642-04898-2\_327

- 68. Higgins, I. et al. beta-vae: Learning basic visual concepts with a constrained variational framework (2016).

- Chollet, F. et al. Keras https://keras.io (2015).

Xilinx. Vivado design suite user guide: High-level synthesis. https://www. xilinx.com/support/documentation/sw\_manuals/xilinx2020\_1/ug902-vivadohigh-level-synthesis.pdf (2020).

- EMP Collaboration. emp-fwk homepage. https://serenity.web.cern.ch/serenity/ emp-fwk/ (2019).

- D'Agnolo, R. T. & Wulzer, A. Learning new physics from a machine. *Phys. Rev. D* 99, 015014 (2019).

#### Acknowledgements

This work is supported by the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant agreement no. 772369) and the ERC-POC programme (grant no. 996696).

#### Author contributions

V.L., M.P., A.A.P., N.G., M.G., S.S., J.D. and Z.W. conceived and designed the hls4ml software library. M.P., T.Q.N. and Z.W. designed and prepared the dataset format. E.G., E.P., T.A., T.J., V.L., M.P., J.N., T.Q.N. and Z.W. designed and implemented autoencoders in hls4ml. E.G., E.P., T.A., T.J., M.P. and J.D. wrote the paper.

#### **Competing interests**

The authors declare no competing interests.

#### Additional information

Extended data is available for this paper at https://doi.org/10.1038/s42256-022-00441-3.

**Correspondence and requests for materials** should be addressed to Ekaterina Govorkova. **Peer review information** *Nature Machine Intelligence* thanks the anonymous reviewers for their contribution to the peer review of this work.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© The Author(s), under exclusive licence to Springer Nature Limited 2022

## NATURE MACHINE INTELLIGENCE

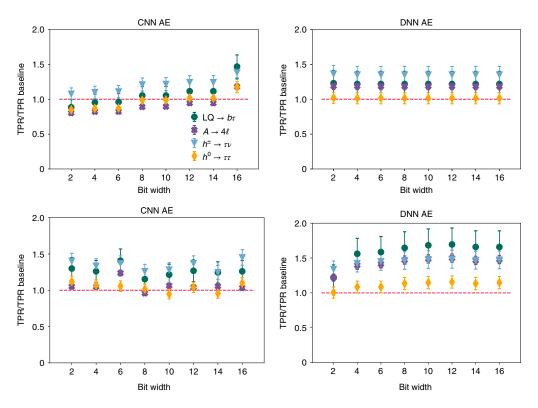

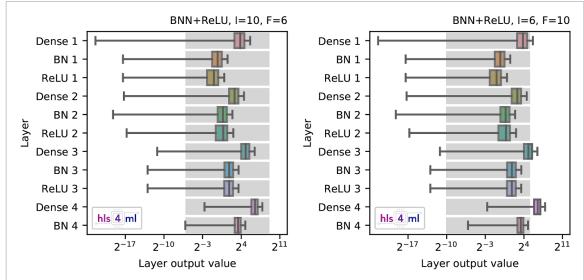

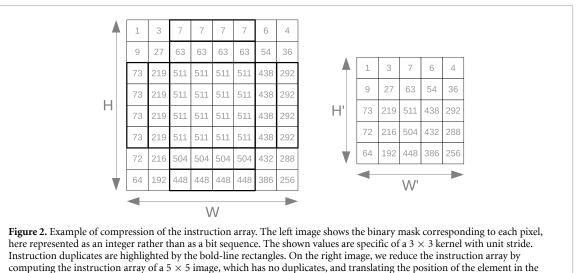

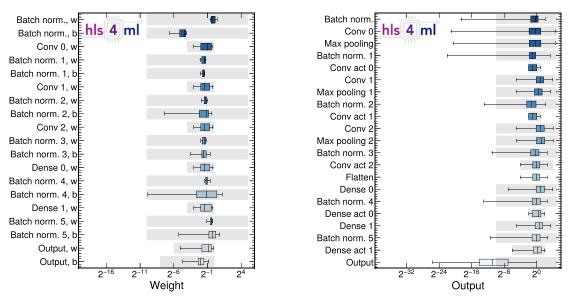

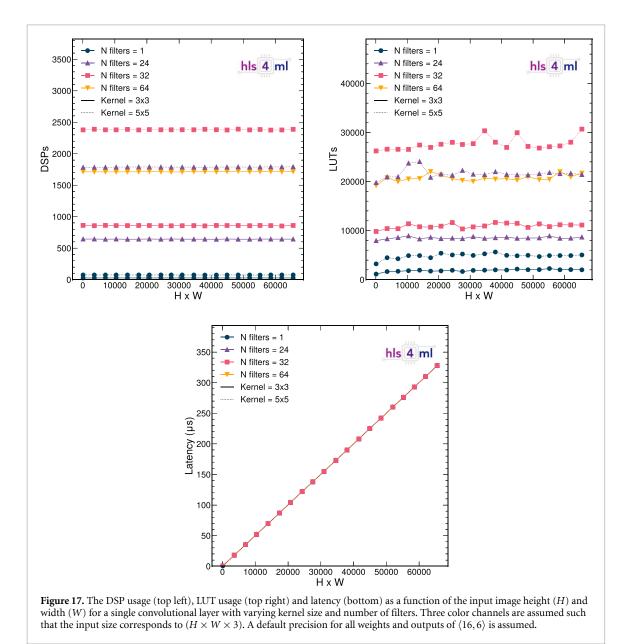

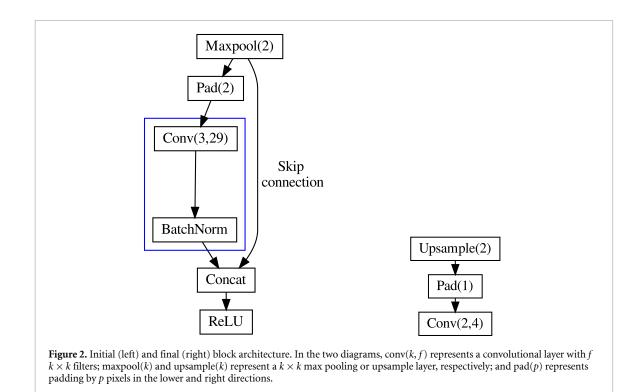

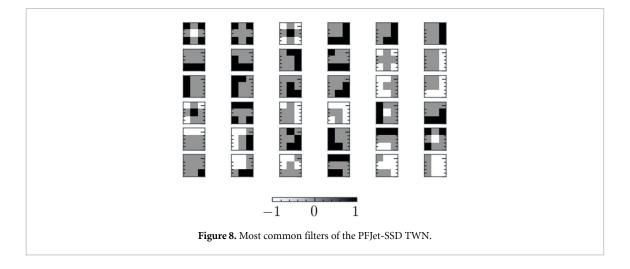

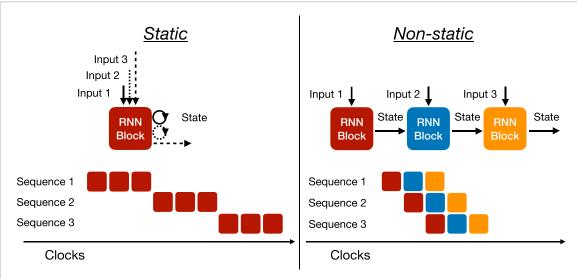

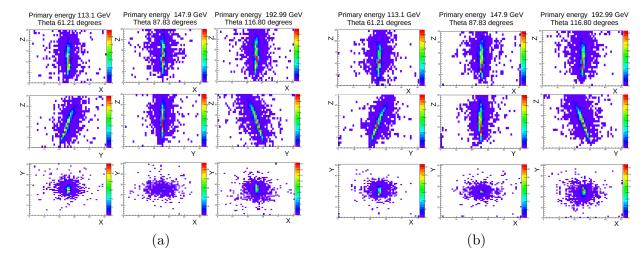

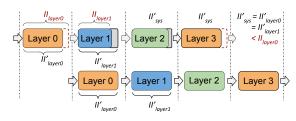

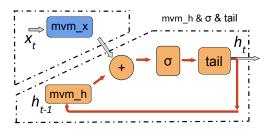

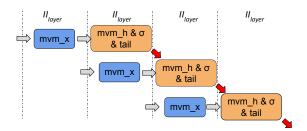

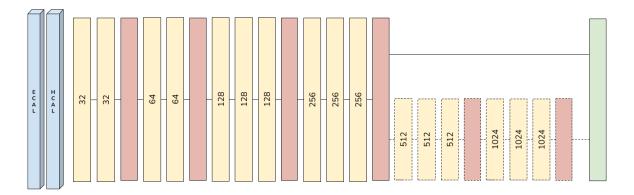

**Extended Data Fig. 1** | Network architectures. Network architecture for the DNN AE (top) and CNN AE (bottom) models. The corresponding VAE models are derived introducing the Gaussian sampling in the latent space, for the same encoder and decoder architectures (see text).

ARTICLES

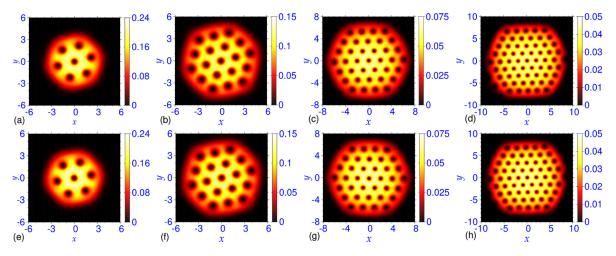

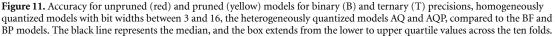

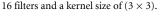

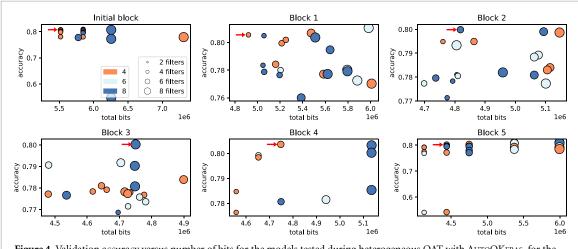

**Extended Data Fig. 2 | TPR ratios for different bit width.** TPR ratios versus model bit width for the VAE CNN (left) and DNN (right) models tested on four new physics benchmark models, using  $D_{\kappa L}$  as figure of merit for PTQ (top) and QAT (bottom) strategies.

Check for updates

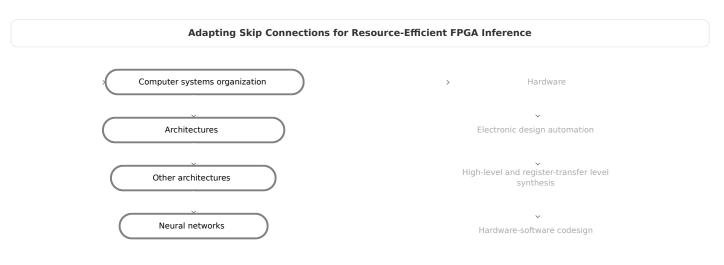

# Automatic heterogeneous quantization of deep neural networks for low-latency inference on the edge for particle detectors

Claudionor N. Coelho Jr<sup>1</sup>, Aki Kuusela<sup>2</sup>, Shan Li<sup>2</sup>, Hao Zhuang<sup>2</sup>, Jennifer Ngadiuba<sup>3</sup>, Thea Klaeboe Aarrestad<sup>4</sup>, Vladimir Loncar<sup>4,5</sup>, Maurizio Pierini<sup>4</sup>, Adrian Alan Pol<sup>4</sup> and Sioni Summers<sup>4</sup>

Although the quest for more accurate solutions is pushing deep learning research towards larger and more complex algorithms, edge devices demand efficient inference and therefore reduction in model size, latency and energy consumption. One technique to limit model size is quantization, which implies using fewer bits to represent weights and biases. Such an approach usually results in a decline in performance. Here, we introduce a method for designing optimally heterogeneously quantized versions of deep neural network models for minimum-energy, high-accuracy, nanosecond inference and fully automated deployment on chip. With a per-layer, per-parameter type automatic quantization procedure, sampling from a wide range of quantizers, model energy consumption and size are minimized while high accuracy is maintained. This is crucial for the event selection procedure in proton-proton collisions at the CERN Large Hadron Collider, where resources are strictly limited and a latency of  $\mathcal{O}(1)$  µs is required. Nanosecond inference and a resource consumption reduced by a factor of 50 when implemented on field-programmable gate array hardware are achieved.

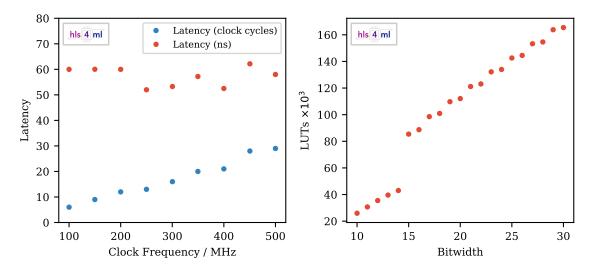

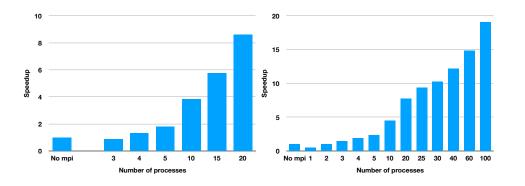

ith edge computing, real-time inference of deep neural networks (DNNs) on custom hardware has become increasingly relevant. Smartphone companies are incorporating artificial intelligence (AI) chips in their design for on-device inference to improve user experience and tighten data security, and the autonomous vehicle industry is turning to application-specific integrated circuits (ASICs) to keep the latency low. Although the typical acceptable latency for real-time inference in applications like those above is O(1) ms (refs. <sup>1,2</sup>), other applications may require submicrosecond inference. For example, high-frequency trading machine learning (ML) algorithms are running on field-programmable gate arrays (FPGAs) to make decisions within nanoseconds<sup>3</sup>. At the extreme inference spectrum end of both the low latency (as in high-frequency trading) and limited area (as in smartphone applications) is the processing of data from proton-proton collisions at the Large Hadron Collider (LHC) at CERN<sup>4</sup>. In the particle detectors around the LHC ring, tens of terabytes of data per second are produced from collisions occurring every 25 ns. This extremely large data rate is reduced by a real-time event filter processing system-the trigger-which decides whether each discrete collision event should be kept for further analysis or be discarded. Data are buffered close to the detector while the processing occurs, with a maximum latency of  $\mathcal{O}(1)$  µs to make the trigger decision. High selection accuracy in the trigger is crucial to keep only the most interesting events while keeping the output bandwidth low, reducing the event rate from 40 MHz to 100 kHz. In 2027, the LHC will be upgraded from its current state, capable of producing up to one billion proton-proton collisions per second, to the so-called High Luminosity-LHC (HL-LHC)<sup>5</sup>. This will involve increasing the number of proton collisions occurring every second by a factor of

five to seven, ultimately resulting in a total amount of accumulated data one order of magnitude higher than what is possible with the current collider. With this extreme increase, ML solutions are being explored as fast approximations of the algorithms currently in use to minimize the latency and maximize the precision of tasks that can be performed.

Hardware used for real-time inference in particle detectors usually has limited computational capacity due to size constraints. Incorporating resource-intensive models without a loss in performance poses a great challenge. In recent years, many developments have aimed at providing efficient inference from an algorithmic point of view. This includes compact network design<sup>6-10</sup>, weight and filter pruning<sup>11,12</sup> or quantization. In post-training quantization<sup>13-17</sup>, the pre-trained model parameters are translated into lower-precision equivalents. However, this process is, by definition, lossy, and it sacrifices model performance. Therefore, solutions to do quantization-aware training have been suggested<sup>18-27</sup>. In these, a fixed numerical representation is adopted for the whole model, and the model training is performed enforcing this constraint during weight optimization. More recently<sup>28-31</sup>, it has been argued that some layers may be more accommodating for aggressive quantization, whereas others may require more expensive arithmetic. This suggests that per-layer heterogeneous quantization is the optimal way to achieve higher accuracy at low resource cost, but it may require further specialization of hardware resources.

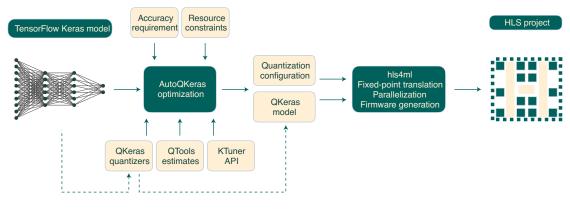

In this Article, we introduce a novel workflow for finding the optimal heterogeneous quantization per layer and per parameter type for a given model, and deploy that model on FPGA hardware. Through minimal code changes, the model footprint is minimized while retaining high accuracy, and then

<sup>&</sup>lt;sup>1</sup>Palo Alto Networks, Palo Alto, CA, USA. <sup>2</sup>Google LLC, Mountain View, CA, USA. <sup>3</sup>California Institute of Technology (Caltech), Pasadena, CA, USA. <sup>4</sup>European Organization for Nuclear Research (CERN), Geneva, Switzerland. <sup>5</sup>Institute of Physics, Belgrade, Serbia. <sup>Senemail:</sup> thea.aarrestad@cern.ch

## NATURE MACHINE INTELLIGENCE

translated into low-latency firmware. This Article makes the following contributions:

- We implement a range of quantization methods in a common library, providing a broad base from which optimal quantizations can easily be sampled.

- We introduce a novel method for finding the optimal heterogeneous quantization for a given model, resulting in minimum area or minimum power DNNs while maintaining high accuracy.

- We have made these methods available online in easy-to-use libraries, called QKeras and AutoQKeras<sup>60</sup>, where simple drop-in replacement of Keras<sup>32</sup> layers makes it straightforward for users to transform Keras models to their equivalent deep heterogeneously quantized versions, which are trained quantization-aware. Using AutoQKeras, a user can trade off accuracy by model size reduction (for example, area or energy).

- We have added support for quantized QKeras models in the library, hls4ml<sup>13</sup>, which converts these pre-trained quantized models into highly parallel FPGA firmware for ultralow-latency inference.

To demonstrate the substantial practical advantages of these tools for high-energy physics and other inference on the edge applications:

- We conduct an experiment consisting of classifying events in an extreme environment, namely the triggering of proton-proton collisions at the CERN LHC, where resources are limited and a maximum latency of O(1)µs is imposed.

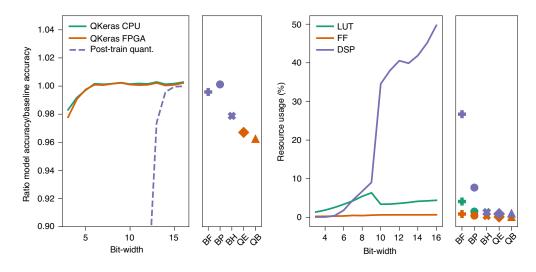

- We show that inference within 60 ns and a reduction of the model resource consumption by a factor of 50 can be achieved through automatic heterogeneous quantization, while maintaining similar accuracy (within 3% of the floating-point model accuracy).

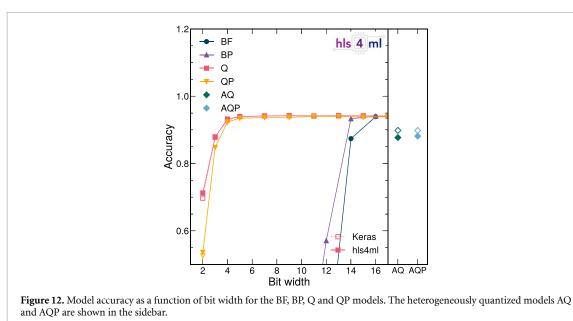

- We show that the original floating-point model accuracy can be maintained for homogeneously quantized DNNs down to a bit-width of six while reducing resource consumption by up to 75% through quantization-aware training with QKeras.

The proposed pipeline provides a novel, automatic end-to-end flow for deploying ultralow-latency, low-area DNNs on chip. This will be crucial for the deployment of ML models on FPGAs in particle detectors and other fields with extreme inference and low-power requirements.

In the remainder of the Article we discuss previous work related to model quantization and model compression with a focus on work related to triggering in particle detectors, we uncover the novel library for training ultralow-latency optimally heterogeneously quantized DNNs (QKeras), we describe the procedure of automatic quantization for optimizing model size and accuracy simultaneously and, finally, we deploy these optimally quantized QKeras models on an FPGA and evaluate their performance.

#### Motivation

The hardware triggering system in a particle detector at the CERN LHC is one of the most extreme environments in which one can imagine deploying DNNs. Latency is restricted to  $O(1) \mu s$ , governed by the frequency of particle collisions and the number of on-detector buffers. The system consists of a limited amount of FPGA resources, all of which are located in underground caverns 50–100 m below the ground surface, where they work on thousands of different tasks in parallel. Because of the high number of tasks being performed, limited cooling capabilities, limited space in the cavern and the limited number of processors, algorithms must be kept as resource-economic as possible. To minimize the latency and maximize the precision of tasks that can be performed in the hardware trigger, ML solutions are being explored as fast approximations of the algorithms currently in use. To simplify the implementation

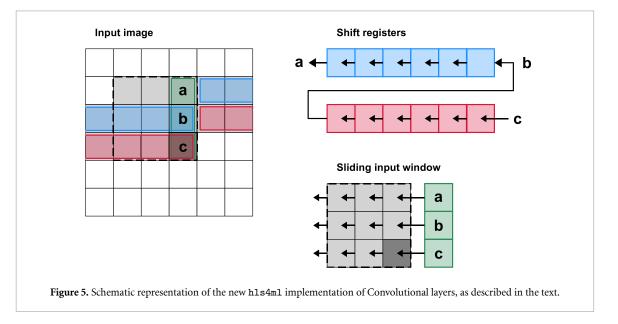

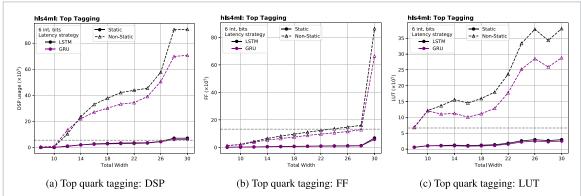

of these, a general library for converting pre-trained ML models into FPGA or ASIC firmware has been developed—hls4ml<sup>13</sup>. The package comprises a library of optimized C++ code for common network layers, which can be synthesized through a high-level synthesis (HLS) tool. Converters are provided for multiple model formats, like TensorFlow<sup>33</sup>, Keras<sup>32</sup>, PyTorch<sup>34</sup> and ONNX<sup>35</sup>.

Although there are other libraries for the translation of ML models to FPGA firmware, as summarized in refs. <sup>36–39</sup>, hls4ml targets extreme low-latency inference to stay within the strict constraints of  $\mathcal{O}(1)$  µs imposed by the hardware trigger systems. In addition, the unique aspect of hls4ml is the support for multiple HLS-vendor backends like Xilinx Vivado HLS, Intel Quartus HLS<sup>40</sup> and Mentor Catapult HLS<sup>41</sup>, all of which are in use at the LHC experiments. The Vivado HLS backend is the most advanced and therefore the one used in this Article.

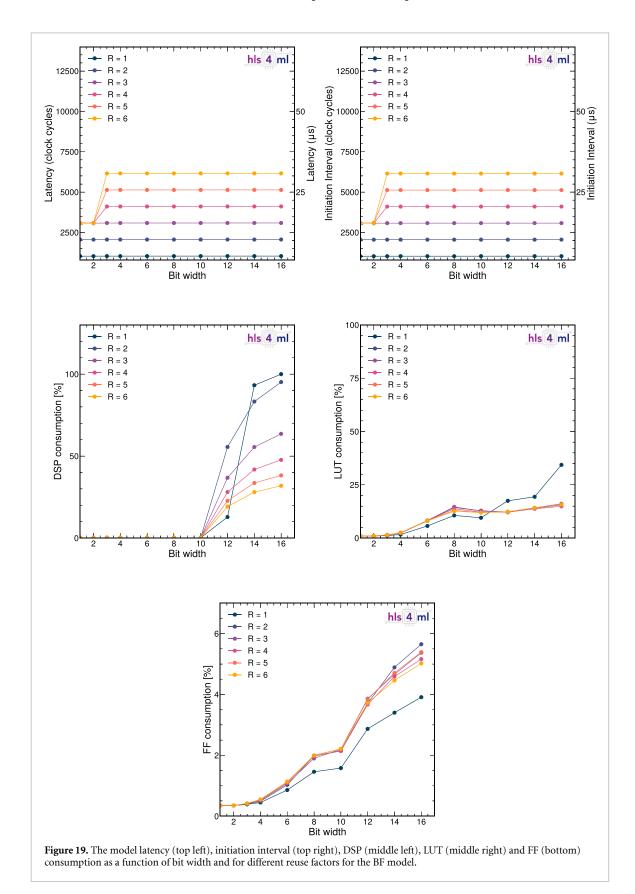

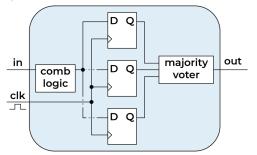

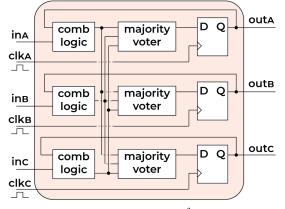

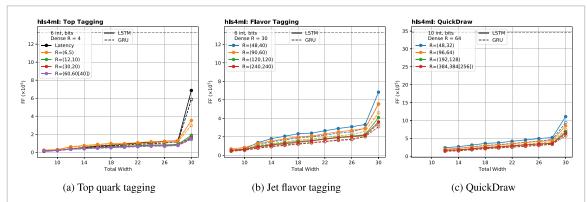

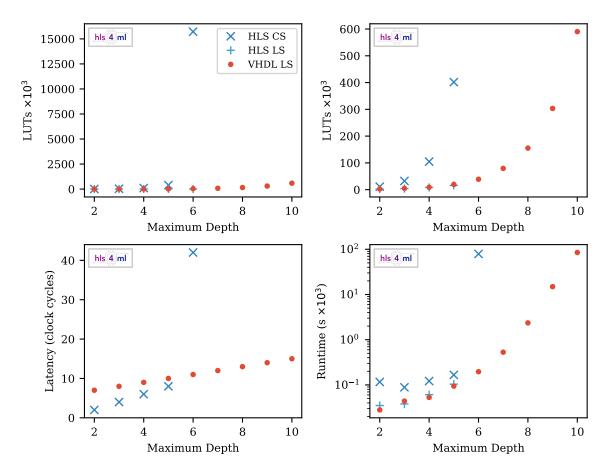

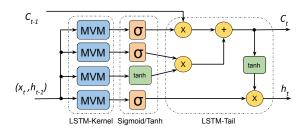

The hls4ml inference architecture is introduced in ref.<sup>13</sup>. A model-specific, layer-unrolled architecture is used to produce ultralow-latency, resource-efficient inference engines for particle physics. The computation for each NN layer is carried out in distinct hardware elements of the target device, which allows for high computational throughput through the layer pipeline, as well as a fine-grained configuration of each layer (including quantization). A simple handle, named 'Reuse Factor' enables users to control the parallelization of the computation, again at a per-layer level. In the fully parallel model, using a Reuse Factor of 1, each individual multiplication of the NN layers is carried out on different resources (whether FPGA digital signal processors (DSPs) or lookup tables (LUTs)). With a Reuse Factor greater than 1, multiplication elements are reused sequentially to reduce the resource cost, at the expense of latency and throughput. This simple handle enables rapid design space exploration as well as configurability to target-specific constraints in the available resources, latency and throughput.

In addition, data access at the NN input and output, as well as data movement between NN layers, can be configured to be fully parallel or fully serial. The former option is used to target ultralow-latency, high-throughput inference in the real-time processing of particle physics experiments, while the latter can be used to fit larger NN models within the available FPGA resources when ultralow latency is not as much of a constraint.

The hls4ml library is implemented as a Python package to facilitate ease of use for non-experts, as well as consistency with other popular deep learning libraries. The first step in the conversion into FPGA firmware consists of translating a given model into an internal representation of the network graph. During this conversion, user-specified optimization configurations are attached to the model, such as the choice of quantization and parallelization. The internal representation is written out into an HLS project, assigning the appropriate layers of the target NN and the user configuration. This HLS project can then be synthesized with the FPGA vendor tools, generating an IP core that can be used in the target application. Many commonly used NN layers are supported: Dense, Convolution, BatchNormalization and several Activation layers. In addition, domain-specific layers can be easily added, one example being compressed distance-weighted graph networks<sup>42</sup>.

In hls4ml, the precision used to represent weights, biases, activations and other components is configurable through post-training quantization, replacing the floating-point values by lower-precision fixed-point ones. This allows compression of the model size, but to some extent sacrifices accuracy. Recently, support for binary and ternary precision DNNs<sup>43</sup> trained quantization-aware has been included in the library. This greatly reduces the model size, but requiring such an extremely low precision of each parameter type sacrifices accuracy and generalization.

As demonstrated in refs. <sup>28–31</sup>, mixed-precision quantization (that is, keeping some layers at higher precision and some at lower precision) is a promising approach to achieve smaller models with high

# ARTICLES

| Model           | Precision         |         |         |         |         |         |                   |         |  |

|-----------------|-------------------|---------|---------|---------|---------|---------|-------------------|---------|--|

|                 | Dense             | ReLU    | Dense   | ReLU    | Dense   | ReLU    | Dense             | Softmax |  |

| BF/BP           | (14, 6)           | (14, 6) | (14, 6) | (14, 6) | (14, 6) | (14, 6) | (14, 6)           | (14, 6) |  |

| BH <sup>a</sup> | w:(8, 3) b:(4, 2) | (13, 7) | (7, 2)  | (10, 5) | (5, 2)  | (8, 4)  | w:(7, 3) b:(4, 1) | (16, 6) |  |

Table 1 | Per-layer quantization for post-training quantized models

When different precision is used for weights and biases, the quantization is listed as w and b, respectively

accuracy. However, finding the optimal heterogeneous quantization per layer and per parameter type, here referred to as 'quantization configuration, is extremely challenging, with the search space increasing exponentially with the number of layers in a model<sup>30</sup>. A solution for finding the mixed quantization configuration that yields the best generalization and accuracy using the Hessian spectrum is proposed in ref. <sup>30</sup>. For ML applications in hardware triggering systems, the resources one has at disposal, as well as the minimum tolerable model accuracy, are usually known. Finding the best model for a given task is therefore a fine compromise between the desired model compression and accuracy with respect to the floating-point-based model. Both factors must be considered when tuning quantization. The goal of this work is thus to provide a method for finding the optimal mixed-precision configuration for a given model, accounting for both the desired model size and accuracy when optimizing the architecture, and to transform these into highly parallel firmware for ultralow-latency inference on chip.

#### **Related work**

Closely related to the work presented here are the FINN<sup>44</sup> and FINN-R<sup>45</sup> frameworks from Xilinx Research Labs, which aim to deploy quantized neural networks on Xilinx FPGAs. The same group have also developed a library for quantization-aware training, Brevitas<sup>46</sup>, based on PyTorch model formats. The LogicNets design flow<sup>47</sup>, also from Xilinx Research Labs, allows for the training of quantized DNNs that map to highly efficient Xilinx FPGA implementations. A comparison between the approach presented here and LogicNets is provided in the section 'Ultralow-latency, quantized model on FPGA hardware'. The FP-DNN48 framework takes TensorFlow<sup>33</sup>-described DNNs as input and maps them onto FPGAs. The open-source alternative, DNNWeaver<sup>49</sup>, automatically generates accelerator Verilog code using optimized templates. Other frameworks focusing on the mapping of convolutional architectures onto efficient hardware design include Snowflake<sup>50</sup>, fpgaConvNet<sup>51-53</sup> and ref. <sup>54</sup>. For other work on FPGA DNN inference, we refer to refs. <sup>36-39,55</sup>. TensorFlow Lite<sup>56</sup> is a set of tools for on-device inference with low latency and small binary sizes, targeting mobile, embedded and Internet of Things (IoT) devices. Currently, TensorFlow Lite supports deployment on Android and iOS devices, embedded Linux and microcontrollers.

Our approach differs from those above with its emphasis on being a multi-backend tool, embracing a fully on-chip design to target the microsecond latency imposed in physics experiments. The hls4ml library is completely open-source, and aims to provide domain scientists with easy-to-use software for deploying highly efficient ML algorithms on hardware.

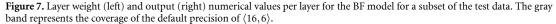

In HAQ<sup>28</sup>, a hardware-aware automated framework for quantization is introduced. The automization procedure consists of computing the curvature of the weight space of a layer, assuming a low curvature will require a lower bit precision for the weights. Our approach differs from HAQ by combining reduced bit precision with filter or neuron unit tuning, where the number of filters or neurons can be automatically tuned during the scan. In this case, the problem becomes highly nonlinear, and we therefore take advantage of an AutoML-type of approach. A Bayesian optimization or randomized search is performed to find a solution that encompasses the precision used for the weights and activations, and the number of units or filters of the layer.

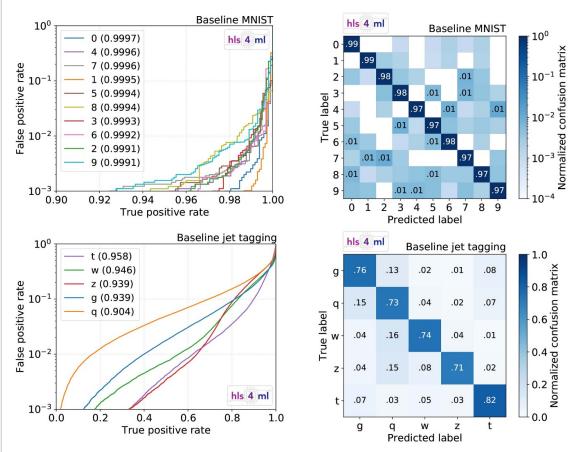

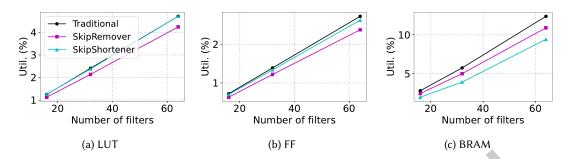

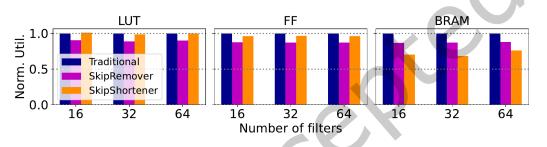

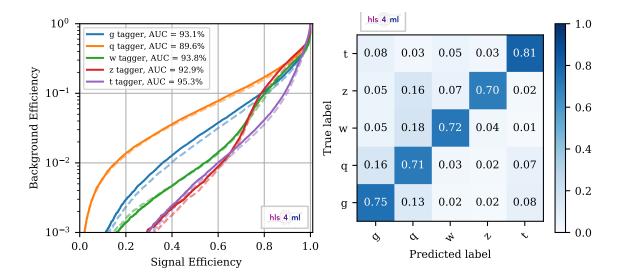

#### Particle identification in the hardware trigger

A crucial task performed by the trigger system that could be greatly improved by a ML algorithm, both in terms of latency and accuracy, is the identification and classification of particles coming from each proton–proton collision. In this Article, we analyse the publicly available dataset introduced in refs. <sup>13,57</sup>. Here, a dataset<sup>58</sup> for the discrimination of jets, a collimated spray of particles, stemming from the decay and/or hadronization of five different particles was presented. This consists of quark (q), gluon (g), W boson, Z boson and top (t) jets, each represented by 16 physics-motivated high-level features. In ref. <sup>13</sup>, this dataset was used to train a DNN for deployment on a Xilinx FPGA. This model was compressed through post-training quantization to further reduce the FPGA resource consumption and provides a baseline to measure the benefits of quantization-aware training with heterogeneous quantization, over post-training quantization.

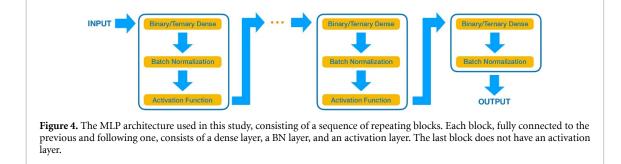

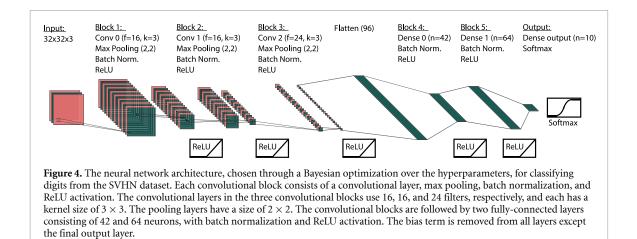

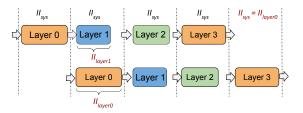

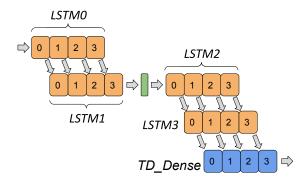

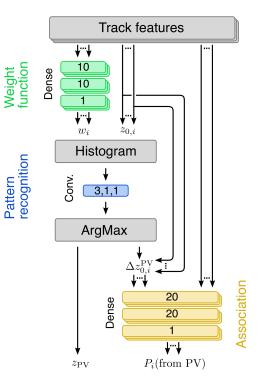

Adopting the same architecture as in ref. <sup>13</sup>, we use a fully connected neural network consisting of three hidden layers (64, 32 and 32 nodes, respectively) with rectified linear unit (ReLU) activation functions. The architecture is shown in Extended Data Fig. 1. The output layer has five nodes, yielding a probability for each of the five classes through a softmax activation function. The model definition in TensorFlow Keras is given in Listing 1.

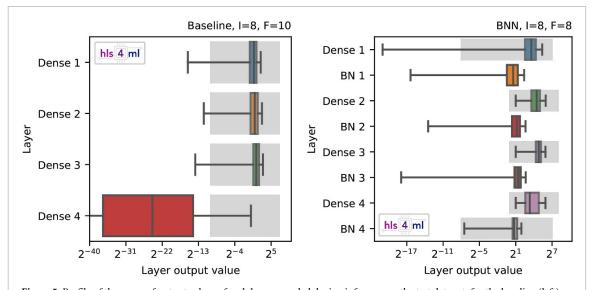

As in ref. <sup>13</sup>, the weights of this network are homogeneously quantized post-training to a fixed-point precision yielding the best compromise between accuracy, latency and resource consumption. This is found to be a fixed-point precision, or bit-width, of 14 bits with 6 integer bits, in the following referred to as  $\langle 14, 6 \rangle$ . We refer to this configuration as the baseline full model (BF). We then train a second pruned version of the BF model, here referred to as baseline pruned (BP). This model has 70% of its weights set to zero through an iterative process where small weights are removed using the TensorFlow Pruning application programming interface<sup>59</sup>, following ref. <sup>13</sup>. This reduces the model size and resource consumption considerably, as all zero-multiplications are excluded during the firmware implementation. We then create one heterogeneously quantized version of the BP model, where each layer is quantized independently post-training to yield the highest accuracy possible at the lowest resource cost. We start with an initial configuration of the model quantization using a wide bit-width, then iteratively reduce the bit-width until reaching a threshold in accuracy loss relative to the initial floating-point model, evaluated on the training set. We iterate over the model in layer order, finding the appropriate precision for weights, biases and output of a given layer, before moving to the next. We apply a more strict threshold in accuracy for earlier layers, because each round of precision reduction only degrades the accuracy. In this case we restrict to a 1% accuracy difference in the first layer, loosening to 2% for the final layer. This model is referred to as the baseline heterogeneous (BH) model. A summary of the per-layer quantizations for the baselines is provided in Table 1.

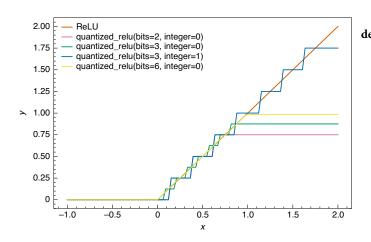

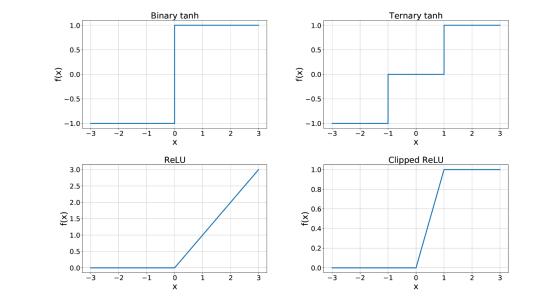

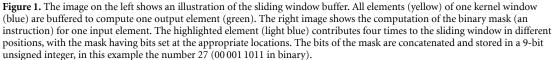

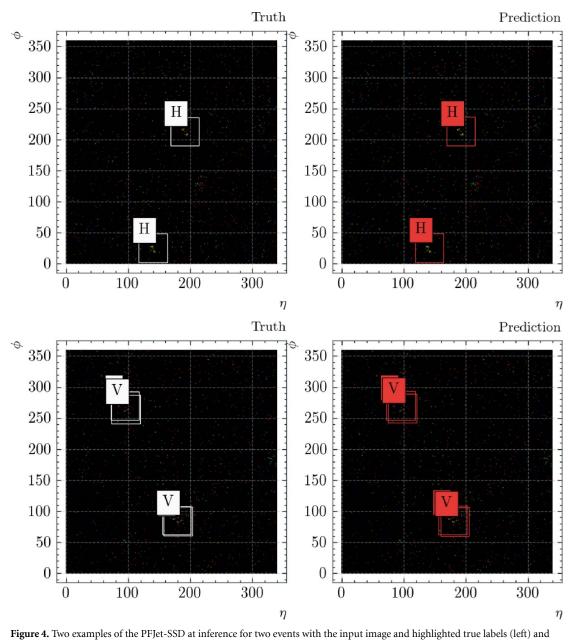

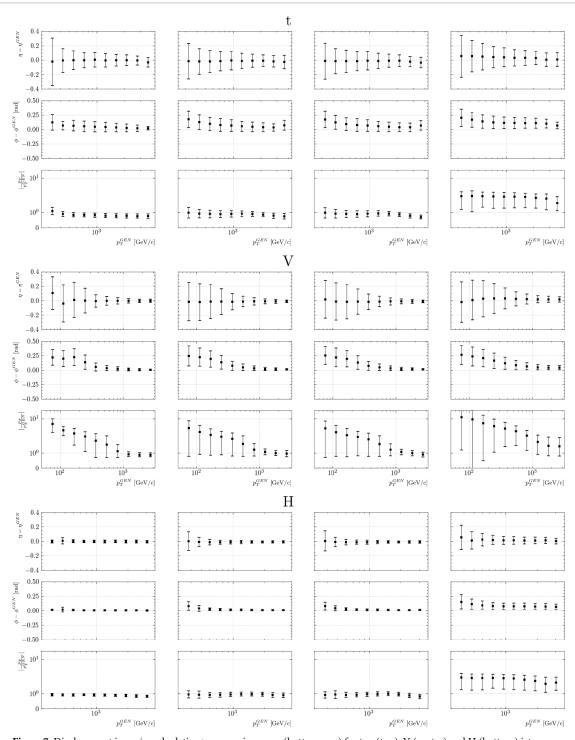

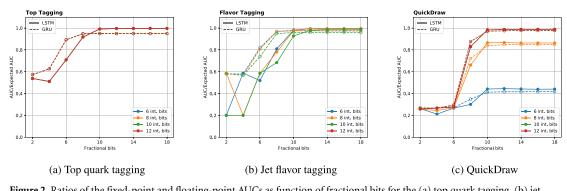

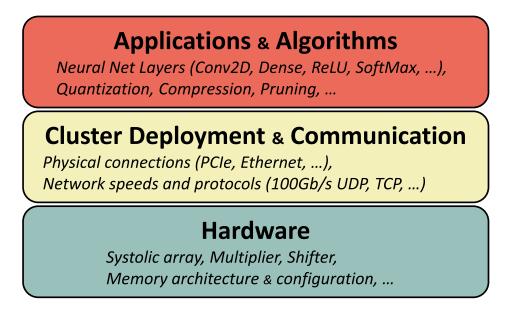

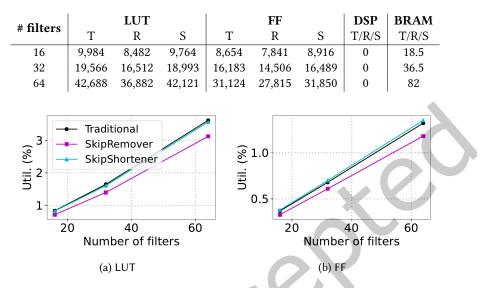

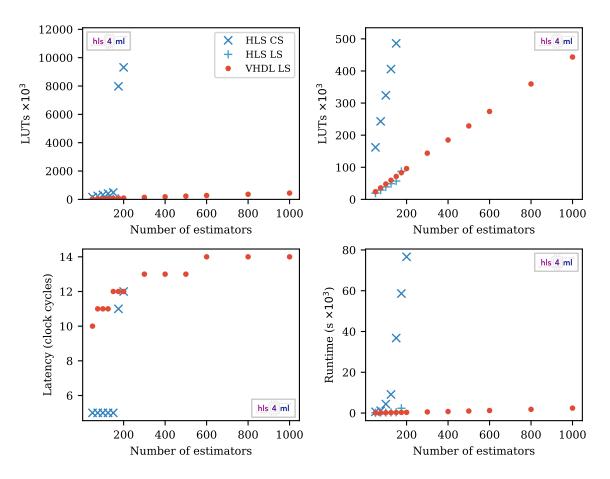

**Fig. 1 | Quantized ReLU function in QKeras.** The quantized\_relu function as implemented in QKeras for 2-bit (purple), 3-bit (green and blue) and 6-bit (yellow) precision and for 0 or 1 integer bits. The unquantized ReLU function is shown for comparison (orange).

From ref.<sup>13</sup>, we know that a post-training quantization of this model results in a degradation in model accuracy. The smaller the model footprint is made through post-training quantization, the larger the accuracy degradation becomes. To overcome this, we develop a novel library that, through minimal code changes, allows us to create deep heterogeneously quantized versions of the Keras model, trained quantization-aware.

In addition, as the amount of available resources on chip is known in advance, we want to find the optimal model for a given use-case allowing a trade-off between model accuracy and resource consumption. We therefore design a method for performing automatic quantization, minimizing the model area while maximizing accuracy simultaneously through a novel loss function. These solutions, simple heterogeneous quantizationaware training and automatic quantization are explained in the following sections.

Keras<sup>32</sup> is a high-level application programming interface designed for building and training deep learning models. It is used for fast prototyping, advanced research and production. To simplify the procedure of quantizing Keras models, we introduce QKeras<sup>60</sup>: a quantization extension to Keras that provides a drop-in replacement for layers performing arithmetic operations. This allows for efficient training of quantized versions of Keras models.

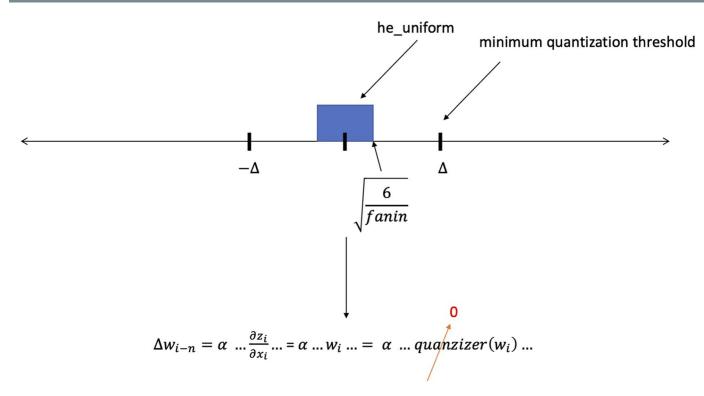

QKeras is designed using the design principle of Keras-that is, being user-friendly, modular, extensible and minimally intrusive to Keras native functionality. The code is based on the work of refs. 18,22, but provides a substantial extension to these. This includes providing a richer set of layers (for instance, including ternary and stochastic ternary quantization), extending the functionality by providing functions to aid the estimation of model area and energy consumption, allowing for simple conversion between non-quantized and quantized networks, and providing a method for performing automatic quantization. Importantly, the library is written in such a way that all the QKeras layers maintain a true drop-in replacement for Keras ones so that minimal code changes are necessary, greatly simplifying the quantization process. During quantization, QKeras uses the straight-through estimator<sup>19</sup>, where the forward pass applies the quantization functions and the backward pass assumes the quantization as the identity function to make the gradient differentiable.

For the model in Listing 1, creating a deep quantized version requires just a few code changes. An example conversion is shown in Listing 2.

Listing 1. Defining a model in Keras: TensorFlow Keras model definition

from tensorflow.keras.layers import Input from tensorflow.keras.layers import Dense, Activation

from tensorflow.keras.layers import BatchNormalization

- x = Input((16))

- x = Dense(64)(x)

- x = BatchNormalization()(x)

- x =Activation('relu')(x)

- x = Dense(32)(x)

- x = BatchNormalization()(x)

- x =Activation('relu')(x)

- x = Dense(32)(x)x = BatchNormalization()(x)

- x = Activation('relu')(x)

- x = Dense(5)(x)

- x = Activation('softmax')(x)

#### Obtaining optimal heterogeneous quantization

The necessary code modifications consist of typing Q in front of the original Keras data manipulation layer name and specifying the appropriate quantization type, for instance, the kernel\_quantizer and bias\_quantizer parameters in a QDense layer. We change only data manipulation layers that perform some form of computation that may change the data input type and create variables (trainable or not). Data transport layers, namely layers performing some form of change of data ordering, without modifying the data itself, remain the same, for example Flatten. When quantizers are not specified, no quantization is applied to the layer and it behaves as the unquantized Keras layer. The only exception is the QBatchNormalization layer. Here, when no quantizers are specified, a power-of-2 quantizer is used for the trainable parameters of the batch normalization layer,  $\gamma$  and  $\beta$ , as well as for the emperical variance  $\sigma$ , while the emperical mean  $\mu$  remains unquantized. This has worked best when attempting to implement quantization efficiently in hardware and software ( $\gamma$  and  $\sigma$  become shift registers and  $\beta$  maintains the dynamic range aspect of the centre parameter)

Listing 2. Defining a model in QKeras: quantized QKeras model example.

from tensorflow.keras.layers import Input, Activation from gkeras import guantized\_bits from gkeras import QDense, QActivation from qkeras import QBatchNormalization x = Input((16)) $x = QDense(64, kernel_quantizer = quantized_bits(6,0,alpha=1)),$ bias\_quantizer = quantized\_bits(6,0,alpha=1))(x) x = QBatchNormalization()(x) $x = QActivation('quantized_relu(6,0)')(x)$  $x = QDense(32, kernel_quantizer = quantized_bits(6,0,alpha=1)),$ bias\_quantizer = quantized\_bits(6,0,alpha=1))(x) x = OBatchNormalization()(x)x = QActivation(`quantized relu(6,0)')(x) $x = QDense(32, kernel_quantizer = quantized_bits(6, 0, alpha=1)),$ bias\_quantizer = quantized\_bits(6,0,alpha=1))(x) x = QBatchNormalization()(x) $x = QActivation('quantized_relu(6,0)')(x)$  $x = QDense(5, kernel_quantizer = quantized_bits(6,0,alpha=1),$ bias\_quantizer = quantized\_bits(6,0,alpha=1))(x) x =Activation('softmax')(x) The second code change is to pass appropriate quantizers, for

example quantized\_bits. In the example above, QKeras is instructed to quantize the kernel and bias to a bit-width of 6 and 0 integer bits. The parameter alpha can be used to change the absolute scale of the weights while keeping them discretized within the chosen bit-width. For example, in a binary network, rather than using the representations  $\pm 1$ , one can use  $\pm alpha$ . In QKeras, by setting

# ARTICLES

alpha='auto', we also allow for the value of alpha to be computed during training from the absolute scale of the weights in question. Further details are provided in the Methods and illustrated in Extended Data Fig. 2.